# Chapter 11

#### Clocks, Watchdog Timer / Timers Read Sections 12-16 of Data Sheet for PIC18F46K20

Updated: 4/19/19

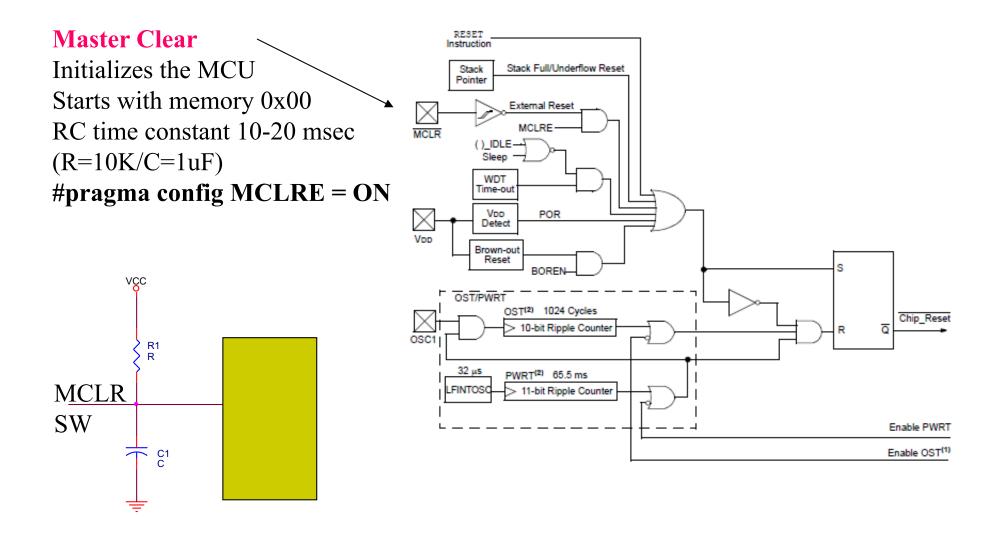

#### **Reset Conditions**

# Watchdog Timer

- □ The watchdog timer is a device that resets the microcontroller if it is allowed to expire.

- □ The watchdog timer is programmable to expire between 4 ms and 131 seconds.

- The watchdog timer is restarted with a ClrWdt() function inC-Language to reset it so it does not expire and cause a reset.

| C statement                  | Assembly Language | Scaling factor | Time to Reset |  |

|------------------------------|-------------------|----------------|---------------|--|

| #pragma config WDTPS = 1     | _WDTPS_1_2H       | 1:1            | 4 ms          |  |

| #pragma config WDTPS = 32768 | _WDTPS_32768_2H   | 1:32768        | 131.072 sec   |  |

#### WD Example

□ Example of how WD operates:

- Make sure you RELEASE the program on the DEMO board

- As you reset (GND) RB0 the WD will expire and thus the program keeps resetting → RD1 blinks.

- □ The time it takes for the WD to be enabled depends on the value of CONFIG2H register (WDTPS) (1024 x 4msec = 5sec) → When RB0 9s set for about 5 seconds later the WD will be enabled, resetting the program:

#define PBO PORTBbits.RBO

#pragma config WDTPS = 1024

#### void main (void)

TRISD = 0b00000000;

// P01

INTCON2bits.RBPU = 0;

// ena

WPUBbits.WPUB0 = 1;

// ena

ANSELH = 0x00;

// ANS

TRISBbits.TRISB0 = 1;

// P01

// PORTD bits 7:0 are all outputs (0)

// enable PORTB internal pullups

// enable pull up on RB0

// AN8-12 are digital inputs (AN12 on P

// PORTB bit 0 (connected to switch) is

```

//setting the WD registers

RCON = 0b0001000;

WDTCON = 1;

```

PORTDbits.RD1 = 1; // This indicates that program just reset Delay1KTCYx(500);

#### while(1)

```

ClrWdt();

PORTDbits.RD1 = 0; // Clear RD1

PORTDbits.RD0 = ~PORTDbits.RD0;

Delay1KTCYx(500);

while (PB0 == 0)

PORTDbits.RD0 = PB0;

```

#### Automatic Wakeup!

/In this program the LED blinks for a few seconds and then the program goes to sleep for about 10 seconds. Then, it wakes up, following watchdog trigger.

#define PBO PORTBbits.RBO #pragma config WDTPS = 2048 // about 10 sec. unsigned char count = 0; void main (void) TRISD = Ob00000000;// PORTD bits 7:0 are all outputs (0) INTCON2bits.RBPU = 0; // enable PORTB internal pullups WPUBbits.WPUBO = 1; // enable pull up on RBO ANSELH =  $0 \times 00$ ; // AN8-12 are digital inputs (AN12 on RBO) TRISBbits.TRISBO = 1; // PORTB bit 0 (connected to switch) is input (1) //setting the WD registers RCON = Ob0001000;WDTCON = 1;PORTDbits.RD1 = 1; // This indicates that program just reset DelaylKTCYx(100); while(1) £ ClrWdt();count = count + 1;PORTDbits.RD1 = 0; // Clear RD1 PORTDbits.RDO = ~PORTDbits.RDO; Delay1KTCYx(20); // Note that if delay must be within 5 sec WD time while (PB0 == 0) PORTDbits.RDO = PBO; if (count == 20)

Measure the current when the board is in sleep mode!

□ Where does the program start when it wakes up?

#### Brownout Reset

- □ The brownout reset is programmed and used to reset the microcontroller if the power supply voltage drops below a pre-programmed value.

- □ The brownout reset triggers the microcontroller and waits at the reset state until the power supply voltage returns to a level higher then the programmed brownout voltage.

| C language               | Assembly Language | Brownout Voltage |

|--------------------------|-------------------|------------------|

| #pragma config BORV = 45 | _BORV_45_2L       | 4.5 V            |

| #pragma config BORV = 42 | _BORV_42_2L       | 4.2 V            |

| #pragma config BORV = 27 | _BORV_27_2L       | 2.7 V            |

| #pragma config BORV = 20 | _BORV_20_2L       | 2.0 V            |

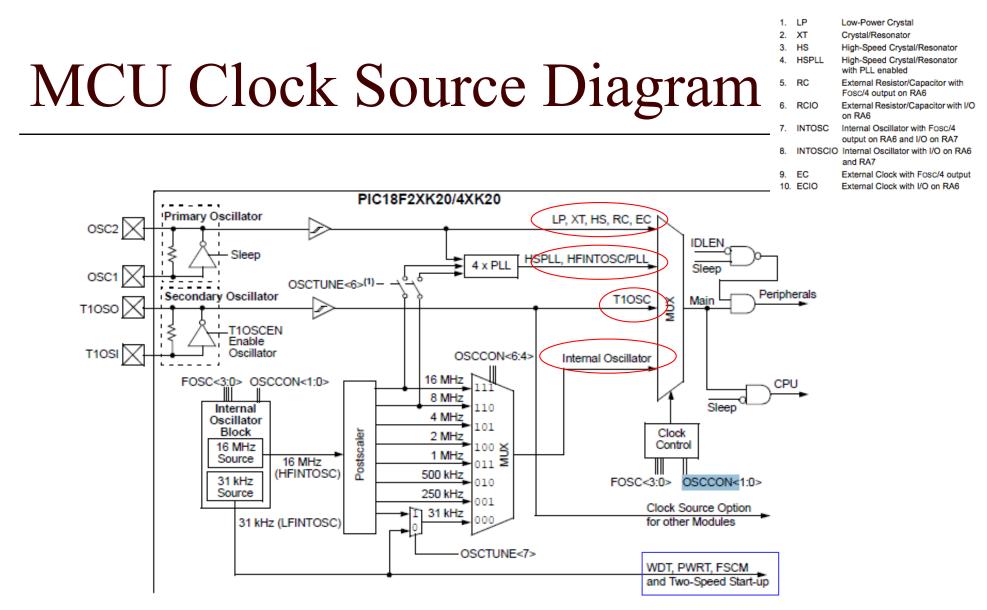

#### Clocks

- The PIC18 family allows many different clocking modes for operation. Some include internal timing and some external.

- External timing sources are very accurate and are crystal- or resonator-based. A less accurate, but less expensive timing source is an RC circuit. An oscillator module or external timing signal can also be used for the microcontroller.

### **Clock Sources**

- Low power crystal (LP) **Examples** of 2. Crystal or ceramic resonator (XT) External XTL or ceramic 3. High-speed crystal or ceramic resonator (HS) Resonator (OSC1/OSC2) 4. High-speed crystal or ceramic resonator with PLL (HSPLL) 5. External resister/capacitor with Fosc/4 output on OSC2 (RC) 6. External resister/capacitor with I/O on OSC2 (RCIO) 7. \*Internal oscillator with Fosc/4 on RA6 and I/O on RA7 (INTIO1) 8. \*Internal oscillator with I/O on RA6 and RA7 (INTIO2) 9. External clock with Fosc/4 (EC) 10. External clock with I/O on RA6 (ECIO)

- □ \*some versions do not have an internal oscillator and

- □ some versions may have additional modes

Note 1: Operates only when HFINTOSC is the primary oscillator.

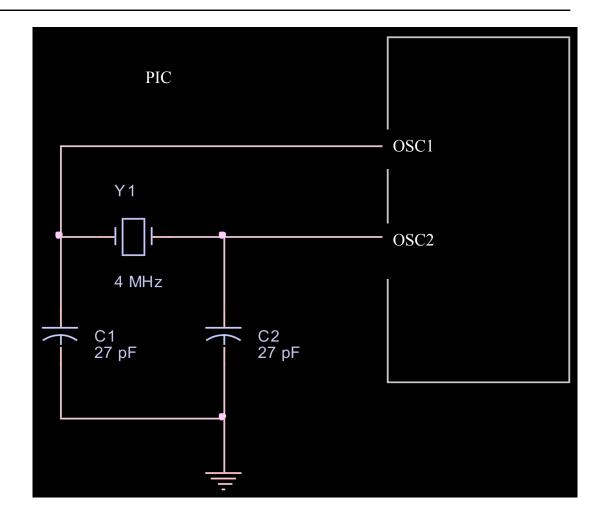

#### XTL / Ceramic Clock Source Connection

PLL internal function Allows multiplying the External clock by 4; This is used to reduce the EMI (Electromagnetic Interference) on the board

#### RC Oscillator Clock Source Connection

External resister/capacitor with Fosc/4 output on OSC2 (RC)

2 MHz operation is attained with R = 3.9Kand C = 30 pF, Fosc/4 is 500 KHz with these values Frequency = 1/[RC(4.2)]; can vary slightly External clock source Connected to OSC1

#### **Clock Examples**

- □ #pragma config OSC = HS // high speed crystal oscillator

- □ #pragma config OSC = RC // RC oscillator

- □ #pragma config OSC = INTIO1 // internal oscillator

| Г                       | R/W-0    | R/W-0           | R/W-1                      | R/W-1        | R-q                 | R-0     | R/W-0      | R/W-0                                                |                                                                                                                            |

|-------------------------|----------|-----------------|----------------------------|--------------|---------------------|---------|------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                         | IDLEN    | IRCF2           | IRCF1                      | IRCF0        | OSTS <sup>(1)</sup> | IOFS    | SCS1       | SCS0                                                 |                                                                                                                            |

| t                       | it 7     |                 |                            |              |                     |         |            | bit 0                                                |                                                                                                                            |

| (                       | DSCCON   | J Reg           | gister                     |              |                     | bit 7   | 1 =        |                                                      | bit<br>Idle mode on SLEEP instruction<br>Sleep mode on SLEEP instruction                                                   |

| 1.                      | LP       | Low-P           | ower Crys                  | tal          |                     | bit 6-4 |            |                                                      | al Oscillator Frequency Select bits                                                                                        |

| 2. XT Crystal/Resonator |          |                 |                            |              |                     |         |            |                                                      | INTOSC drives clock directly)                                                                                              |

| 3.                      | HS       | High-S          | Speed Crys                 | tal/Resona   | ator                |         | 10         | 0 = 8 MHz<br>1 = 4 MHz                               |                                                                                                                            |

| 4.                      | HSPLL    | -               | Speed Crys                 |              | ator                |         | 01:        | 0 = 2 MHz<br>1 = 1 MHz <sup>(3)</sup><br>0 = 500 kHz |                                                                                                                            |

| 5.                      | RC       |                 | al Resistor<br>4 output or |              | r with              | bit 3   | 00         |                                                      | n either HFINTOSC/512 or LFINTOSC directly) <sup>(2)</sup><br>tart-up Time-out Status bit <sup>(1)</sup>                   |

| 6.                      | RCIO     | Extern<br>on RA | al Resistor                | /Capacitor   | with I/O            |         | 1 =<br>0 = | Device is runni<br>Device is runni                   | ing from the clock defined by FOSC<2:0> of the CONFIG1 register<br>ing from the internal oscillator (HFINTOSC or LFINTOSC) |

| 7.                      | INTOSC   |                 | al Oscillato               | r with Fos   | c/4                 | bit 2   |            |                                                      | Frequency Stable bit<br>equency is stable                                                                                  |

|                         |          | output          | on RA6 ar                  | nd I/O on F  | RA7                 |         |            |                                                      | equency is not stable                                                                                                      |

| 8.                      | INTOSCIO | Interna         | al Oscillato               | r with I/O o | on RA6              | bit 1-0 |            | S<1:0>: System<br>= Internal oscilla                 | Clock Select bits                                                                                                          |

|                         |          | and R           | A7                         |              |                     |         |            |                                                      | imer1) oscillator                                                                                                          |

| 9.                      | EC       |                 | al Clock w                 | ith Fosc/4   | output              |         | 00         | = Primary clock                                      | (determined by CONFIG1H[FOSC<3:0>]).                                                                                       |

| 10                      |          |                 | al Clock w                 |              |                     |         |            |                                                      |                                                                                                                            |

## Programming Example

```

#pragma config MCLRE = ON

#pragma config OSC = HS

#pragma config WDT = ON

#pragma config WDTPS = 256

#pragma config BORV = 42

#pragma BOR = ON

```

```

void main(void)

// initialize system here

while(1)

{

```

// enable master clear input

// select crystal oscillator

// set watchdog

// watchdog time is 1 second

// set brownout reset voltage

// brownout is on

// main program loop

ClrWdt();

// reset watchdog

// system software goes here

}

Basic Concepts in Counters and Timers

- □ In digital systems

- Counting is a fundamental concept.

- Clock is an essential element.

- Count is in synchronization with the clock.

- Count is converted in time by multiplying the count and the clock period.

#### Hardware Counters and Timers

- Counter is a register that can be loaded with a binary number (count) which can be decremented or incremented per clock cycle.

- □ Calculating time:

- Find the difference between the beginning count and the last count

- Multiply the count difference by the clock period

- □ The register can also be used as a counter by replacing the clock with a signal from an event.

- □ When a signal from an event arrives, the count in the register is incremented (or decremented); thus, the total number of events can be counted.

# Types of Counters

- □ Up-counter

- Counter is incremented at every clock cycle

- When count reaches the maximum count, a flag is set

- Counter can be reset to zero or to the initial value

- □ Down-counter

- Counter is decremented at every clock cycle

- When count reaches zero, a flag is set

- Counter can be reset to the maximum or the initial value

- □ Free-running counter

- Counter runs continuously and only readable

- When it reaches the maximum count, a flag is set

### **Timer Applications**

- □ Time delay

- □ Pulse wave generation

- Pulse width or frequency measurement

- □ Timer as an event counter

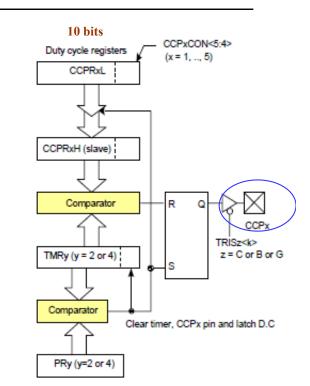

Capture, Compare, and PWM (CCP) Modules

Duty

- □ CCP modules are commonly found in recent<sup>|cycle</sup> microcontrollers

- 16-bit (or two 8-bit) registers specially designed to perform the following functions in conjunction with timers

- □ Capture: The CCP pin can be set as an input to record the arrival time of a pulse.

- □ Compare: The CCP pin is set as an output, and at a given count, it can be driven low, high, or toggled.

- □ Pulse width modulation (PWM): The CCP pin is set as an output and the duty cycle of a pulse can be varied.

- The count for the period and the duty cycle are loaded into CCP registers.

- In this mode, the duty cycle of the output pulse can be varied.

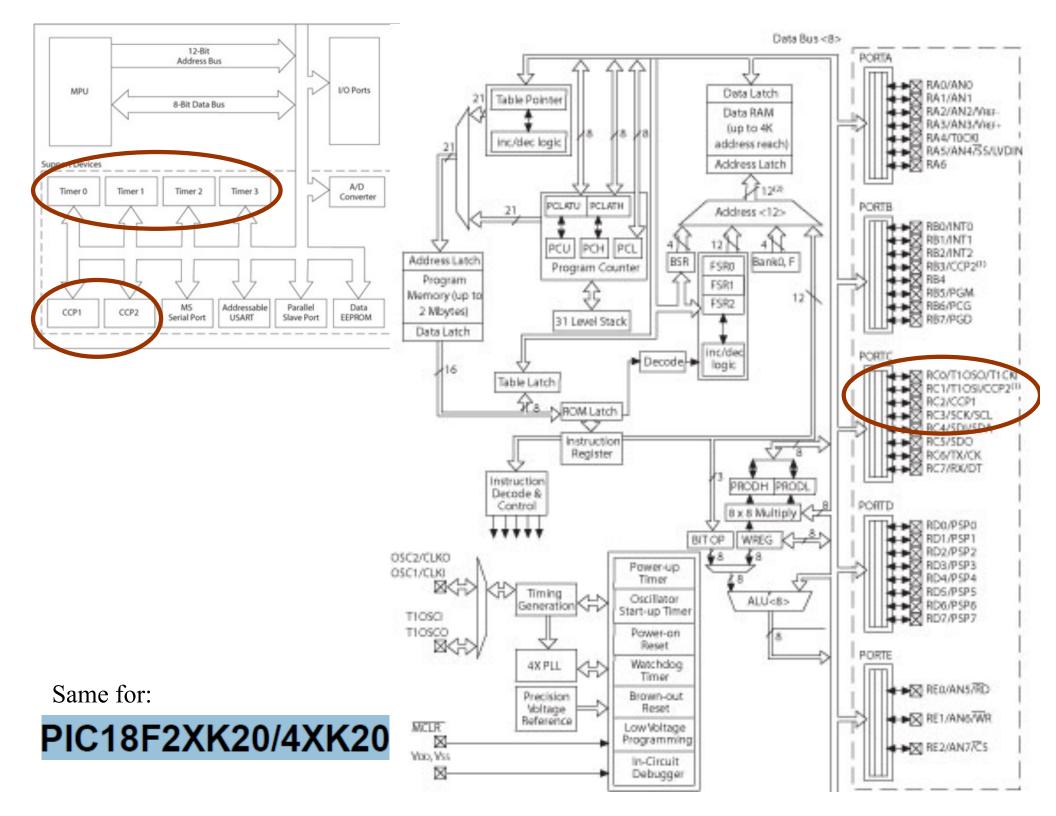

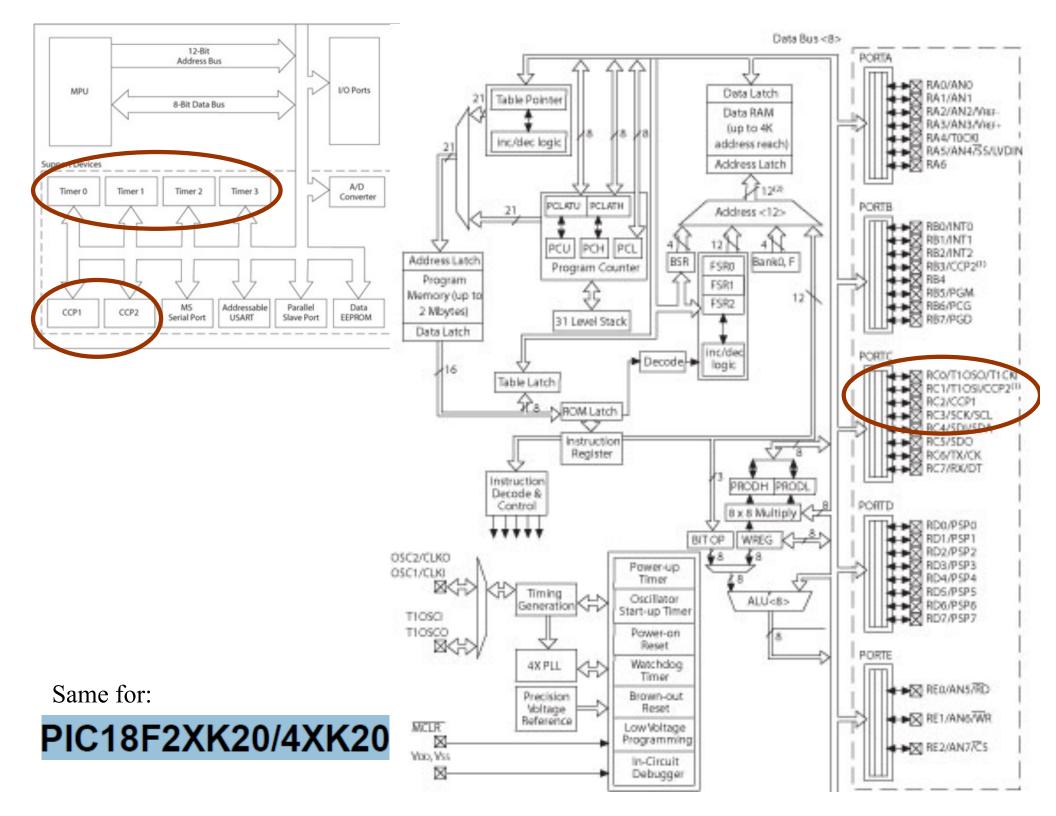

### PIC18 Timers

□ The PIC18 microcontroller have multiple timers, and all of them are up-counters.

12-88

-Rit Data R

UO Ports

- □ Timers are divided into two groups: 8-bit and 16-bit

- □ Labeled as Timer0 to Timer3 or Timer4 (if available)

- Timer0 can be set up as an 8-bit or 16-bit timer.

- **Timer1 and Timer3** are 16-bit timers.

- Timer2 and Timer4 (if available) are 8-bit timers.

- Each timer associated with its Special Function Register (SFR): T0CON-T3CON or T4CON

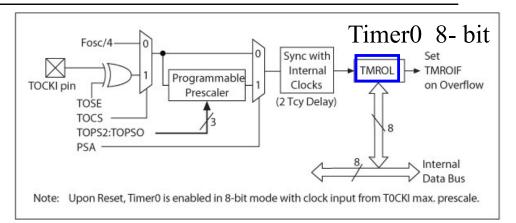

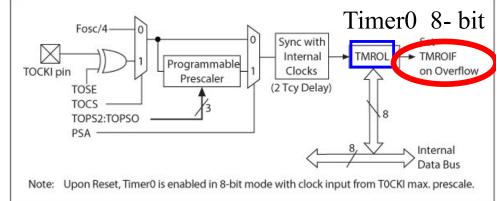

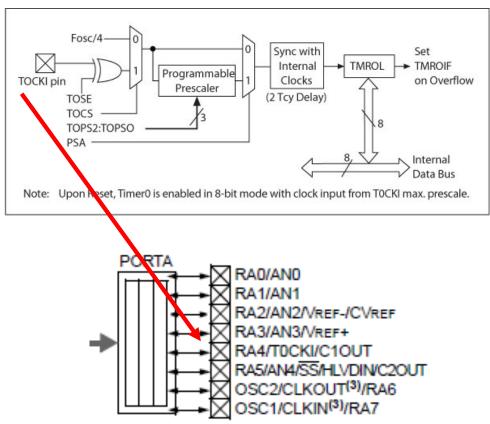

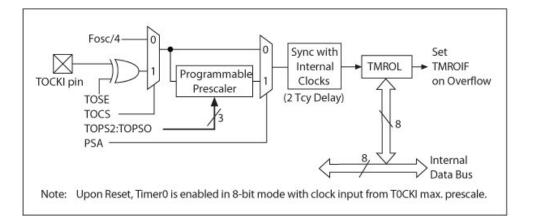

### Timer0

- 1. Can be set up as an 8-bit or 16-bit timer

- 2. Has eight options of pre-scale values (Divides)

- Can run on internal clock source (instruction cycle) or external clock connected to pin RA4/T0CK1

- 4. Generates an interrupt or sets a flag when it overflows from FFH to 00 in the 8-bit mode and from FFFFH to 0000 in the 16-bit mode

- 5. Can be set up on either rising edge or falling edge when an external clock is used

Note: TMR Flags are set when the counter reg. has reached it max.

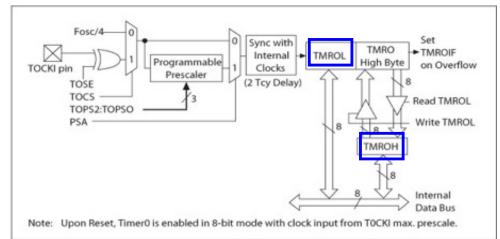

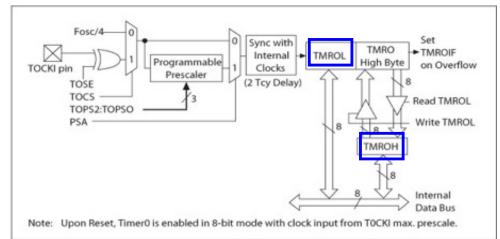

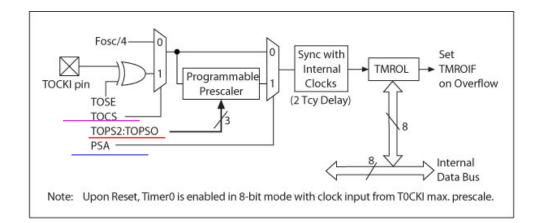

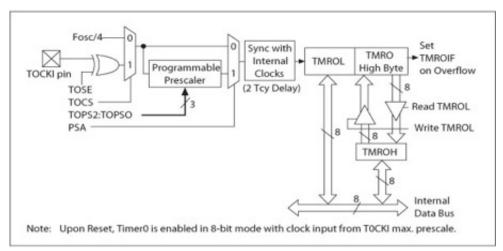

#### Timer0 16-bit

#### Timer0

- 1. Can be set up as an 8-bit or 16-bit timer

- 2. Has eight options of pre-scale values (Divides)

- Can run on internal clock source (instruction cycle) or external clock connected to pin RA4/T0CK1

- 4. Generates an interrupt or sets a flag when it overflows from FFH to 00 in the 8-bit mode and from FFFFH to 0000 in the 16-bit mode

- 5. Can be set up on either rising edge or falling edge when an external clock is used

#### Timer0 16-bit

### **TIMER0** Registers

#### REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7                      | Bit 6                     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 |  |  |  |

|--------|----------------------------|---------------------------|--------|--------|-------|--------|--------|-------|--|--|--|

| TMR0L  | Timer0 Reg                 | Timer0 Register, Low Byte |        |        |       |        |        |       |  |  |  |

| TMR0H  | Timer0 Register, High Byte |                           |        |        |       |        |        |       |  |  |  |

| INTCON | GIE/GIEH                   | PEIE/GIEL                 | TMR0IE | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF  |  |  |  |

| T0CON  | TMR00N                     | T08BIT                    | TOCS   | TOSE   | PSA   | T0PS2  | T0PS1  | T0PS0 |  |  |  |

| TRISA  | RA7 <sup>(1)</sup>         | RA6 <sup>(1)</sup>        | RA5    | RA4    | RA3   | RA2    | RA1    | RA0   |  |  |  |

#### Timer0

- TMROH buffer between internal data bus and TMR0 high byte

- Read from the TMR0L register, the upper half of Timer0 is latched into the TMR0H register

- Ensures that the PIC18 always reads a 16-bit value that its upper byte and lower byte belong to the same time (since only read 8-bits at a time)

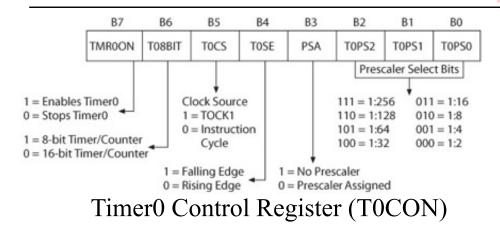

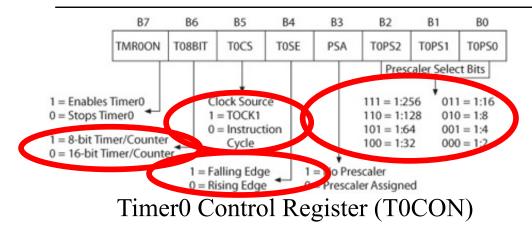

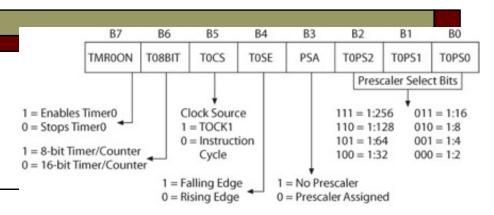

### Timer0 Control Register (1 of 2)

- □ Timer0 as timer

- Bit5 must be cleared to use the internal clock.

- At each instruction cycle (four clock cycles), the timer register is incremented.

- □ Timer0 as a counter

- Bit5 must be set 1 to use an external clock.

- In this mode, input signal at PORTA-pin RA4/T0CK used as a clock.

- When Bit4 = 1, register is incremented on the falling edge, and when Bit4 = 0, the register is incremented on the rising edge.

- □ Prescaler

- Divides clock frequency by a specified ratio.

- To use prescaler, Bit3 = 0, and three bits Bit2-Bit0 specify scaler ratio from 1:2 to 1:256

#### Timer0 Control Register (2 of 2)

#### □ Interrupt

- When Timer0 overflows from FFH to 00 in the 8-bit mode and from FFFFH to 0000 in the16-bit mode, it sets TMR0IF (Timer0 Interrupt Flag) –Bit2 in the INTCON register.

- □ Flag can be used two ways: 1) a software loop can be set up to monitor the flag, or 2) an interrupt can be generated.

- □ Flag must be cleared to start the timer again.

- □ 16-bit mode

- When Timer0 is set in the 16-bit mode, it uses two 8-bit registers TMR0L and TMR0H.

| Name   | Bit 7              | Bit 6                                         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 |  |  |

|--------|--------------------|-----------------------------------------------|--------|--------|-------|--------|--------|-------|--|--|

| TMROL  | Timer0 Reg         | Timer0 Register, Low Byte                     |        |        |       |        |        |       |  |  |

| TMR0H  | Timer0 Reg         | Timer0 Register, High Byte                    |        |        |       |        |        |       |  |  |

| INTCON | GIE/GIEH           | PEIE/GIEL                                     | TMR0IE | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF  |  |  |

| TOCON  | TMR00N             | TMROON T08BIT TOCS TOSE PSA TOPS2 TOPS1 TOPS0 |        |        |       |        |        |       |  |  |

| TRISA  | RA7 <sup>(1)</sup> | RA6 <sup>(1)</sup>                            | RA5    | RA4    | RA3   | RA2    | RA1    | RA0   |  |  |

#### TABLE 12-1: REGISTERS ASSOCIATED WITH TIMER0

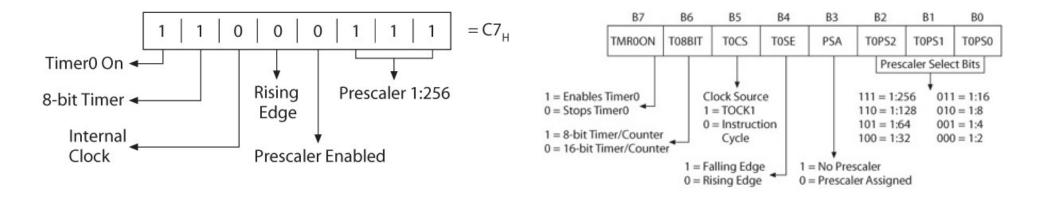

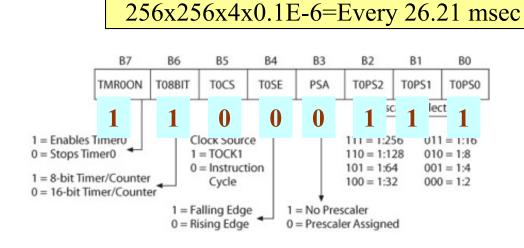

#### Example: Explain the setting

What are the setting if TIMER0 Register is set to C7?

#### Control Word to Initialize Timer0

#### Example - Set TMR0 as an 8-bit timer

- □ Every instruction cycle the register is updated  $\rightarrow$  4x(Clock\_Period)

- □ With a pre-scale=1:256 (divide the clock by 256)→ pre\_scalex4x(Clock\_Period)

- □ 8-bit register allows counting 256 values  $\rightarrow$

- (2^n)x pre\_scalex4x(Clock\_Period)

- □ Assuming using a 10MHz internal clock, rising edge clock, how often the flag is set if timer 0 is set as 8-bit counter? What should TMR0 (TOCON) setup be?

### Example For TMR0 (1)

Using a 16-bit TMR0 generate a high priority interrupt every 1 sec. Assume rising edge, 1:128 prescale, and a 10MHz crystal oscillator (internal clock).

# Example For TMR0 (2)

We can actually design a real-time clock with this!

- □ Using a 16-bit TMR0 generate a high priority interrupt every 1 sec. Assume rising edge, 1:128 pre-scale, and a 10MHz crystal oscillator (internal clock).

- □  $1 \sec/0.4 \sec=2,500,000 \leftarrow$  number of counts that must be generated

- 16 bit → Assume pre-scale 1:128

- 2,500,000/128=19531.25 (up counter) ← number of counts

- $2^{16-1}=65535$ ; (65535)-19531=46,004 → B3B4 → load B3B4 into TMR0L/H and count up to FFFF → then a flag is set!

- □ Code:

- High priority  $\rightarrow$

- $\blacksquare \quad \text{RCON} \rightarrow$

- INTCON→

- INTCON2 $\rightarrow$

- INTCON3→

- PIR1 $\rightarrow$

- TCON→

High priority → ORG 0x08 RCON → IPEN = 1 INTCON→ Set GIEH/L ; PEIE ; TMR0IE ; clear FLAG INTCON2→ set TMR0IP (priority) INTCON3→ All zero PIR1→ clear all flags TCON→ TMR0ON=1 ; T0PS=110 Load B3B4 into TMR0L/H and count up to FFFF → generate interrupt

Note: TMR Flags are set when the counter reg. has reached it max.

#### Example For TMR0 (3)

|          |           |                                                                                       | (-)                          |                                                                    |                          |  |  |  |  |

|----------|-----------|---------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------|--------------------------|--|--|--|--|

| 1        |           |                                                                                       | 2 EX11-2 One Second I        | Delay With Interrupt"                                              |                          |  |  |  |  |

| 2        |           | -                                                                                     | f =inhx32                    |                                                                    |                          |  |  |  |  |

| 3<br>4   | #inclu    | de <p18f4< td=""><td>52.1nc&gt;</td><td>;This is a header file</td><td></td></p18f4<> | 52.1nc>                      | ;This is a header file                                             |                          |  |  |  |  |

| 5        |           | ORG                                                                                   | 00                           |                                                                    | When flag is set the MPU |  |  |  |  |

| 6        |           | GOTO                                                                                  | MAIN                         |                                                                    | transfer the program to  |  |  |  |  |

| 7        |           | 00.0                                                                                  |                              |                                                                    |                          |  |  |  |  |

| 8        |           | ORG                                                                                   | 0×08 <                       |                                                                    | high priority interrupt  |  |  |  |  |

| 9        |           | GOT0                                                                                  | TMR0_ISR                     |                                                                    | vector location 0x08     |  |  |  |  |

| 10       | Г<br>Г    |                                                                                       |                              | L                                                                  |                          |  |  |  |  |

| 11       | MAIN:     | CLRF                                                                                  | INTCON3                      | ;Disable all INT flags                                             |                          |  |  |  |  |

| 12       |           | CLRF                                                                                  | PIR1                         | ;Clear all internal peripheral f                                   | lags                     |  |  |  |  |

| 13<br>14 |           | BSF<br>BSF                                                                            | RCON, IPEN<br>INTCON2,TMRØIP | ;Enable priority - RCON <7><br>;Set Timer0 as high-priority        |                          |  |  |  |  |

| 15       |           | MOVLW                                                                                 | B'11100000'                  | ;Set Timer@ us high-priority<br>;Set Timer@:global interrupt, high |                          |  |  |  |  |

| 16       |           | IORWF                                                                                 | INTCON,1                     | ;piority, overflow, interrupt flag                                 |                          |  |  |  |  |

| 17       |           | MOVLW                                                                                 | B'10000110'                  | ;Enable Timer0: 16-bit, internal                                   |                          |  |  |  |  |

| 18       |           | MOVWF                                                                                 | TØCON                        | ; prescaler- 1:128                                                 | ·                        |  |  |  |  |

| 19       |           |                                                                                       |                              |                                                                    |                          |  |  |  |  |

| 20       | DELAY_1s: |                                                                                       | 0.00                         |                                                                    |                          |  |  |  |  |

| 21       |           | MOVLW                                                                                 | 0xB3                         | ;High count of B3B4H                                               |                          |  |  |  |  |

| 22<br>23 |           | MOVWF<br>MOVLW                                                                        | TMR0H<br>0xB4                | ;Load high count in Timer0<br>;Low count of B3B4H                  |                          |  |  |  |  |

| 24       |           | MOVER                                                                                 | TMRØL                        | ;Load low count in Timer0                                          |                          |  |  |  |  |

| 25       |           | BCF                                                                                   | INTCON, TMRØIF               | ;Clear TIMRO overflow flag ñ Sta                                   | rt counter               |  |  |  |  |

| 26       | HERE :    | GOTO                                                                                  | HERE                         | ;Wait here for an interrupt                                        |                          |  |  |  |  |

| 27       |           |                                                                                       |                              | · · ·                                                              | When the Interrupt       |  |  |  |  |

| 28       |           | ORG                                                                                   | 0x100                        |                                                                    | 1                        |  |  |  |  |

| 29       | TMR0_ISR: |                                                                                       | 0.00                         |                                                                    | service routine is       |  |  |  |  |

| 30       |           | MOVLW<br>MOVWF                                                                        | 0xB3                         | ;High count of B3B4H                                               | executed, the TMR0 is    |  |  |  |  |

| 31<br>32 |           | MOVWE                                                                                 | TMR0H<br>0xB4                | ;Load high count in Timer0<br>;Low count of B3B4H                  | ,                        |  |  |  |  |

| 33       |           | MOVWF                                                                                 | TMRØL                        | ;Load low count in Timer0                                          | reloaded, interrupts are |  |  |  |  |

| 34       |           | BCF                                                                                   | INTCON, TMRØIF               | ;Clear TIMRØ overflow flag ñ Sta                                   | cleared, back to MAIN    |  |  |  |  |

| 35       |           | RETFIE                                                                                | FAST                         | ;Return                                                            |                          |  |  |  |  |

| 36       |           | END                                                                                   | <del>(</del>                 |                                                                    |                          |  |  |  |  |

| 2.7      | -         |                                                                                       |                              |                                                                    |                          |  |  |  |  |

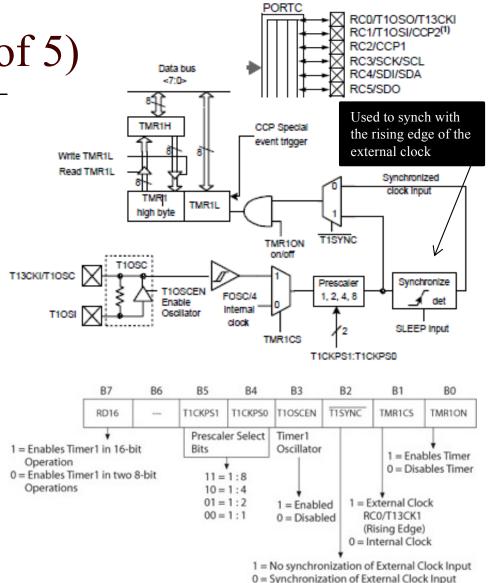

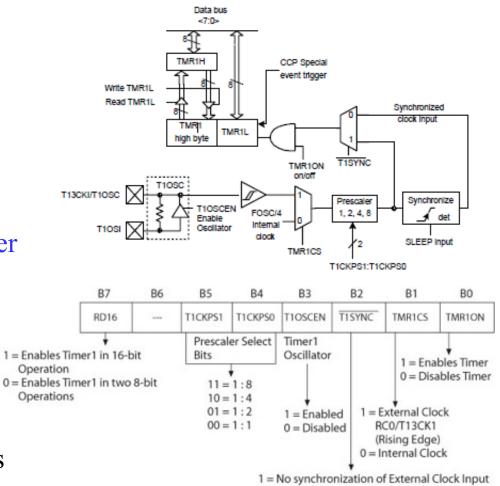

### Timer1 – 16-bit (1 of 5)

- □ A 16-bit counter/timer with two 8-bit registers (TMR1H and TMR1L); both registers are readable and writable

- Four options of prescale value , (Bit5-Bit4)

- Clock source (Bit1) can be internal (instruction cycle) or external (pin RC0/T13CK1) on rising edge

- Sets flag or generates an interrupt when it overflows from FFFFH to 0000

| Name    | Bit 7                | Bit 6                                     | Bit 5      | Bit 4        | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-------------------------------------------|------------|--------------|---------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL                                 | TMROIE     | INTOIE       | RBIE    | TMROIF | INTOIF | RBIF   | 59                         |

| RCON    | IPEN                 | SBOREN                                    | _          | RI           | TO      | PD     | POR    | BOR    | 58                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                                      | RCIF       | TXIF         | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 62                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                                      | RCIE       | TXIE         | SSPIE   | CCP1IE | TMR2IE | MR1IF  | 62                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP                                      | RCIP       | TXIP         | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 62                         |

| PIR2    | OSCFIF               | C1IF                                      | C2IF       | EEIF         | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 62                         |

| PIE2    | OSCFIE               | C1IE                                      | C2IE       | EEIE         | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 62                         |

| IPR2    | OSCFIP               | C1IP                                      | C2IP       | EEIP         | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 62                         |

| TRISB   | PORTB Da             | PORTB Data Direction Control Register     |            |              |         |        |        |        |                            |

| TRISC   | PORTC Da             | PORTC Data Direction Control Register     |            |              |         |        |        |        |                            |

| TMR1L   | Timer1 Reg           | gister, Low E                             | Byte       |              |         |        |        |        | 60                         |

| TMR1H   | Timer1 Reg           | gister, High I                            | Byte       |              |         |        |        |        | 60                         |

| T1CON   | RD16                 | T1RUN                                     | T1CKPS1    | T1CKPS0      | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 60                         |

| TMR3H   | Timer3 Reg           | gister, High I                            | Byte       | •            |         |        |        | •      | 61                         |

| TMR3L   | Timer3 Reg           | gister, Low E                             | Byte       |              |         |        |        |        | 61                         |

| T3CON   | RD16                 | T3CCP2                                    | T3CKPS1    | T3CKPS0      | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 61                         |

| CCPR1L  | Capture/Co           | ompare/PWI                                | M Register | 1, Low Byte  |         |        |        |        | 61                         |

| CCPR1H  | Capture/Co           | Capture/Compare/PWM Register 1, High Byte |            |              |         |        |        |        | 61                         |

| CCP1CON | P1M1                 | P1M0                                      | DC1B1      | DC1B0        | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 61                         |

| CCPR2L  | Capture/Co           | ompare/PWI                                | M Register | 2, Low Byte  |         |        |        |        | 61                         |

| CCPR2H  | Capture/Co           | ompare/PWI                                | M Register | 2, High Byte |         |        |        |        | 61                         |

| CCP2CON | _                    | _                                         | DC2B1      | DC2B0        | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0 | 61                         |

#### REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

#### Timer1 (3 of 5)

- □ Timer1 Operation

- Can operate in three modes:

- $\Box$  timer,

- □ synchronous counter,

- □ asynchronous counter

- Bit0 enables or disables the timer

- When Bit1 = 0, it operates as a timer and increments count at every instruction cycle.

- □ When Bit1 = 1, it operates as a counter and increments count at every rising edge of the external clock.

- When Bit3 = 1, Timer1 oscillator is enabled which is used for low frequency operations.

0 = Synchronization of External Clock Input

#### TMR1 Example

□ Generate 100 usec clock; assuming internal clock is 10MHz (See the handout).

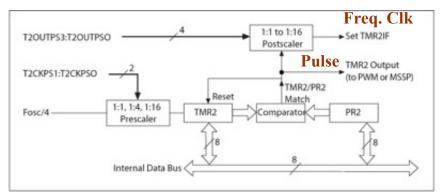

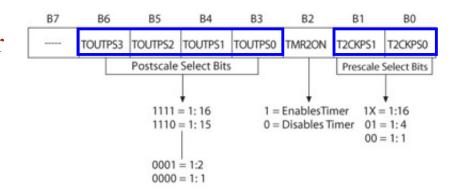

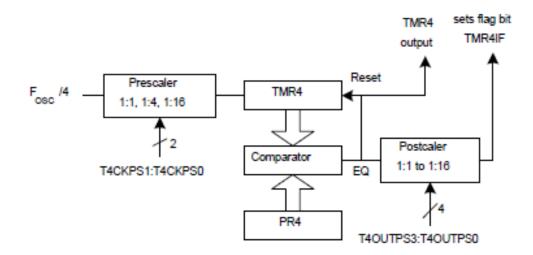

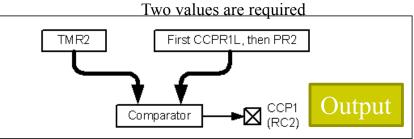

#### Timer2

- □ Two 8-bit registers (TMR2 and PR2)

- □ An 8-bit number is loaded in PR2 and the timer is turned on, which is incremented every instruction cycle.

- □ When the count in the timer register and the PR register match, an output pulse is generated and the timer register is set to zero.

- □ The output pulse goes through a postscaler that divides the frequency by the scale factor and sets the flag TMR2IF-

- Bit1 in the Peripheral Interrupt Register1 (PIR1) that can be used to generate an interrupt.

Master Synchronous Serial Port (MSSP)

#### TMR2

#### REGISTERS ASSOCIATED WITH PWM AND TIMER2

|   | Name    | Bit 7                                     | Bit 6         | Bit 5        | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   |

|---|---------|-------------------------------------------|---------------|--------------|----------|----------|--------|---------|---------|

|   | INTCON  | GIE/GIEH                                  | PEIE/GIEL     | TMR0IE       | INTOIE   | RBIE     | TMR0IF | INTOIF  | RBIF    |

|   | RCON    | IPEN                                      | SBOREN        | _            | RI       | TO       | PD     | POR     | BOR     |

|   | PIR1    | PSPIF <sup>(1)</sup>                      | ADIF          | RCIF         | TXIF     | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  |

|   | PIE1    | PSPIE <sup>(1)</sup>                      | ADIE          | RCIE         | TXIE     | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  |

|   | IPR1    | PSPIP <sup>(1)</sup>                      | ADIP          | RCIP         | TXIP     | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  |

|   | TRISB   | PORTB Da                                  | ata Direction | Control Regi | ster     |          |        |         |         |

|   | TRISC   | PORTC Data Direction Control Register     |               |              |          |          |        |         |         |

|   | TMR2    | Timer2 Reg                                | gister        |              |          |          |        |         |         |

|   | PR2     | Timer2 Per                                | riod Register |              |          |          |        |         |         |

|   | T2CON   | _                                         | T2OUTPS3      | T2OUTPS2     | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| L | CCPR1L  | Capture/Compare/PWM Register 1, Low Byte  |               |              |          |          |        |         |         |

|   | CCPR1H  | Capture/Compare/PWM Register 1, High Byte |               |              |          |          |        |         |         |

|   | CCP1CON | P1M1                                      | P1M0          | DC1B1        | DC1B0    | CCP1M3   | CCP1M2 | CCP1M1  | CCP1M0  |

|   | CCPR2L  | Capture/Compare/PWM Register 2, Low Byte  |               |              |          |          |        |         |         |

|   | CCPR2H  | Capture/Compare/PWM Register 2, High Byte |               |              |          |          |        |         |         |

|   | CCP2CON | _                                         | _             | DC2B1        | DC2B0    | CCP2M3   | CCP2M2 | CCP2M1  | CCP2M0  |

|   | ECCP1AS | ECCPASE                                   | ECCPAS2       | ECCPAS1      | ECCPAS0  | PSSAC1   | PSSAC0 | PSSBD1  | PSSBD0  |

|   | PWM1CON | PRSEN                                     | PDC6          | PDC5         | PDC4     | PDC3     | PDC2   | PDC     | PDC0    |

## Example for Timer2

- □ Generate a periodic high-priority interrupt every 8-msec using Timer2. Assume a 32-MHz crystal oscillator.

- Assume post/pre scaled values are 16

- Loaded value in PR2 will be

Remember, we start with 0 count  $\rightarrow$  -1 is needed

- PR2 = [Td / [Inst. Clock Cycle(4) x Prescaler x PostScaler x clock period)]] 1

- $\square PR2 = [8msec/[4x16x16x(1/32MHZ)]] 1 = 249$

PR2=249 RCON: IPEN=1 IPR1: TMR21P=1; TMR2IF=CLR INTCON=C0; GLOBAL INT T2CON=7E; TMR2 ENABLE AND SCALING SETUP PIE1: TMR2IE=SET

#### Example for Timer2 - continue

#### □ Actual code:

| that TMR2 counts up |

|---------------------|

|                     |

| ipt                 |

| t at high priority  |

|                     |

|                     |

| pt                  |

| escaler to 16, set  |

|                     |

| w interrupt         |

|                     |

PR2=249 RCON: IPEN=1 IPR1: TMR21P=1; TMR2IF=CLR INTCON=C0; GLOBAL INT T2CON=7E; TMR2 ENABLE AND SCALING SETUP PIE1: TMR2IE=SET

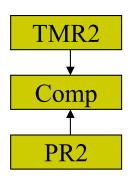

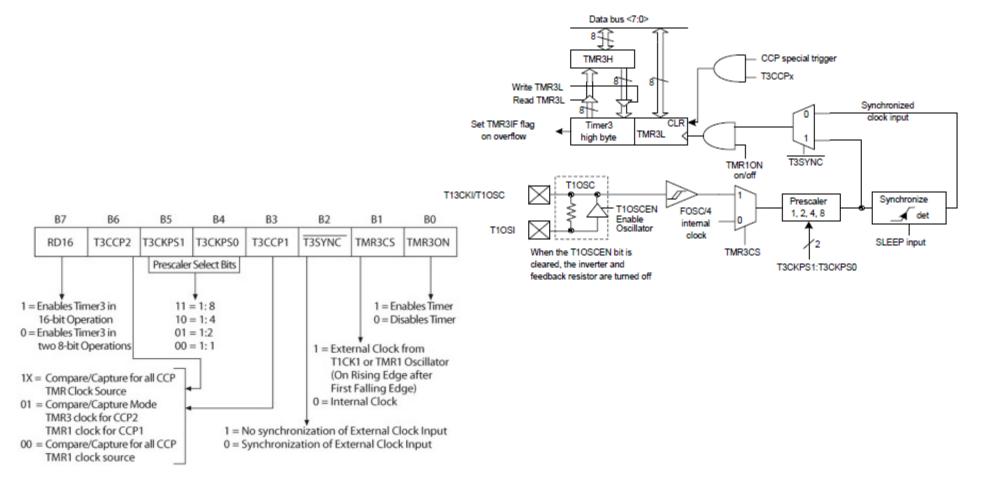

#### Timer3

#### □ Similar to Timer1

#### Timer4

- □ Only available to the PIC18F8X2X and PIC6X2X devices

- □ The value of TMR4 is compared to PR4 in each clock cycle

- □ When the value of TMR4 equals that of PR4, TMR4 is reset to 0

- □ The contents of T4CON are identical to those of T2CON

- □ ....similar to Timer2 (Two 8-bit registers )

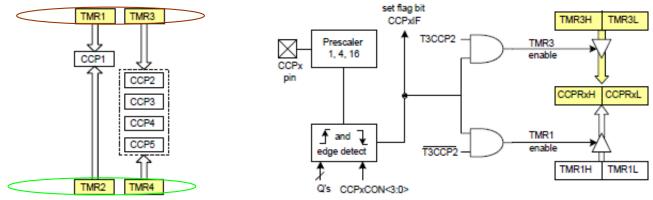

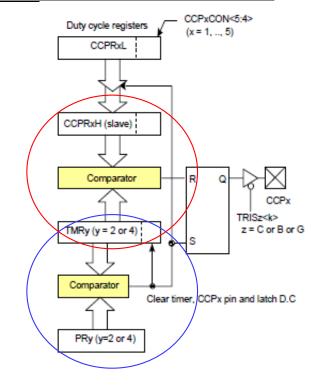

#### CCP & ECCP

# CCP (Capture, Compare, and PWM) Modules

- □ PIC18 Device may have 1, 2, or 5 CCP modules

- Each CCP module requires the use of a timer resource

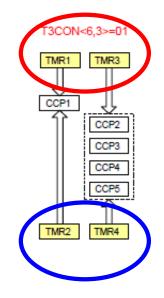

- Capture or compare mode, the CCP module may use either Timer1 or Timer3 to operate.

- PWM mode, either Timer2 or Timer4 may be used

- □ The operations of all CCP modules are identical, with the exception of the special event trigger mode present on CCP1 and CCP2

- □ Each module is associated with

- A control register (CCPxCON)

- A data register (CCPRx) which consists of two 8-bit register: CCPRxL and CCPRxH

- □ The assignment of a particular timer to a module is determined by the bit 6 and bit 3 of the T3CON

| Control   | REGISTER 16-1: CCF                                                                                                                                                           | P1CON: ENHANCED CA                                                                                                                                                                                                  | PTURE/COMPA                                                                                                                                                                                                                 | RE/PWM CO                                                                  | NTROL REG                                          | BISTER                         |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|

| Dogistor  | R/W-0 R/W-0                                                                                                                                                                  | R/W-0 R/W-0                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                       | R/W-0                                                                      | R/W-0                                              | R/W-0                          |

| Register  | P1M1 P1M0                                                                                                                                                                    | DC1B1 DC1B                                                                                                                                                                                                          | CCP1M3                                                                                                                                                                                                                      | CCP1M2                                                                     | CCP1M1                                             | CCP1M0                         |

| (CCP1CON) | bit 7                                                                                                                                                                        | · · ·                                                                                                                                                                                                               | · · ·                                                                                                                                                                                                                       |                                                                            |                                                    | bit 0                          |

|           |                                                                                                                                                                              |                                                                                                                                                                                                                     |                                                                                                                                                                                                                             |                                                                            |                                                    |                                |

|           | Legend:                                                                                                                                                                      |                                                                                                                                                                                                                     |                                                                                                                                                                                                                             |                                                                            |                                                    |                                |

|           | R = Readable bit                                                                                                                                                             | W = Writable bit                                                                                                                                                                                                    | U = Unimpleme                                                                                                                                                                                                               |                                                                            |                                                    |                                |

|           | -n = Value at POR                                                                                                                                                            | '1' = Bit is set                                                                                                                                                                                                    | '0' = Bit is clear                                                                                                                                                                                                          | ed                                                                         | x = Bit is unkn                                    | lown                           |

|           | xx = P1A:<br>If CCP1M<<br>00 = Single<br>Mode<br>01 = Full-b<br>10 = Half-b<br>11 = Full-b<br>ont 5-4 DC1B<1:0:<br>Capture mo<br>Unused.<br>Compare m<br>Unused.<br>PWM mode | e output: P1A, P1B, P1C and<br>e").<br>pridge output forward: P1D mo<br>pridge output: P1A, P1B modu<br>ridge output: P1A, P1B modu<br>ridge output reverse: P1B mo<br>>: PWM Duty Cycle bit 1 and<br>ode:<br>mode: | P1D controlled by st<br>adulated; P1A active;<br>lated with dead-band<br>dulated; P1C active;<br>bit o                                                                                                                      | P1B, P1C inad<br>P1B, P1C inad<br>d control; P1C,<br>P1A, P1D inad         | ection 16.4.7 "I<br>ctive<br>P1D assigned<br>ctive | Pulse Steering<br>as port pins |

|           | 0000 = Ca<br>0001 = Ra<br>0010 = Ca<br>0011 = Ra<br>0100 = Ca<br>0101 = Ca<br>0110 = Ca<br>1000 = Ca<br>1001 = Ca<br>1001 = Ca<br>1010 = Ca<br>1011 = Ca<br>1011 = Ca        | ompare mode, toggle output o                                                                                                                                                                                        | ets ECCP module)<br>n match<br>e<br>edge<br>g edge<br>pin low, set output o<br>pin high, clear output<br>are interrupt only, CC<br>event (ECCP resets<br>igh; P1B, P1D active<br>igh; P1B, P1D active<br>w; P1B, P1D active | It on compare I<br>CP1 pin reverts<br>TMR1 or TMR<br>-high<br>-low<br>high | match (set CCP<br>to I/O state                     | PHIF)                          |

#### REGISTER 15-1: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0 R/W-0 R/W-0 |        | R/W-0  | R/W-0  |

|-------|--------|---------|---------|-------------------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1            | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |                   |        |        | bit 0  |

| R = Readat<br>-n = Value a<br>bit 7 |                                                                                                                                                                                                                                                                                                                  | MI - Dit is set                                                                                          | U = Unimplemented bit          |                            |  |  |  |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------|--|--|--|--|--|

| bit 7                               |                                                                                                                                                                                                                                                                                                                  | '1' = Bit is set                                                                                         | '0' = Bit is cleared           | x = Bit is unknown         |  |  |  |  |  |

|                                     |                                                                                                                                                                                                                                                                                                                  | 6-bit Read/Write Mode Enab<br>bles register read/write of Tin                                            |                                |                            |  |  |  |  |  |

|                                     |                                                                                                                                                                                                                                                                                                                  | eles register read/write of Tim                                                                          |                                |                            |  |  |  |  |  |

| bit 6,3                             | T3CCP<2:1>: Timer3 and Timer1 to CCPx Enable bits<br>1x = Timer3 is the capture/compare clock source for CCP1 and CP2<br>01 = Timer3 is the capture/compare clock source for CCP2 and<br>Timer1 is the capture/compare clock source for CCP1<br>00 = Timer1 is the capture/compare clock source for CCP1 and CP2 |                                                                                                          |                                |                            |  |  |  |  |  |

| bit 5-4                             | T3CKPS<1:0>: Timer3 Input Clock Prescale Select bits                                                                                                                                                                                                                                                             |                                                                                                          |                                |                            |  |  |  |  |  |

|                                     | 10 = 1:4<br>01 = 1:2                                                                                                                                                                                                                                                                                             | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value |                                |                            |  |  |  |  |  |

| bit 2                               | (Not usa<br>When TM                                                                                                                                                                                                                                                                                              | ble if the device clock comes<br>MR3CS = 1:                                                              | ,                              |                            |  |  |  |  |  |

|                                     | 1 = Do not synchronize external clock input<br>0 = Synchronize external clock input                                                                                                                                                                                                                              |                                                                                                          |                                |                            |  |  |  |  |  |

|                                     | When TMR3CS = 0:<br>This bit is ignored. Timer3 uses the internal clock when TMR3CS = 0.                                                                                                                                                                                                                         |                                                                                                          |                                |                            |  |  |  |  |  |

| bit 1                               | TMR3CS: Timer3 Clock Source Select bit                                                                                                                                                                                                                                                                           |                                                                                                          |                                |                            |  |  |  |  |  |

|                                     | fallin                                                                                                                                                                                                                                                                                                           | rnal clock input from Timer1<br>ig edge)<br>mal clock (Fosc/4)                                           | oscillator or T13CKI (on the r | ising edge after the first |  |  |  |  |  |

| bit 0                               | TMR3ON                                                                                                                                                                                                                                                                                                           | I: Timer3 On bit<br>bles Timer3                                                                          |                                |                            |  |  |  |  |  |

# Applications of CCP

- □ Event arrival time recording

- Swimming competition, need to compare different swimmer times

- Period measurement

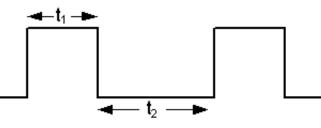

- Capture function configured to capture the timer values corresponding to two consecutive rising or falling edges

- D Pulse width measurement

- Capture function configured to capture two adjacent rising and falling edges

- □ Interrupt generation

- All capture inputs can serve as edge-sensitive interrupt sources

- □ Event counting

- Event represented by signal edge

- CCP channel used in conjunction with a timer or another CCP channel to counter number of events that occur during a timer interval

- □ Time reference

- CCP capture module used with another CCP channel in compare mode

- Detect event, add desired response time, compare mode determine when to activate response

- Duty cycle measurement

- Percentage of time signal is high within a period

### **Basic** operation

- □ Each CCP module is comprised of two 8-bit registers: CCPR1H (high) and CCPR1L (low) → Total of 16-bits

- Called capture and compare register

- □ Can operate as 16-bit Capture register, 16-bit Compare register, or dutycycle PWM register

- Timer1 and Timer3 are used as clock resources for Capture and Compare registers

- Timer2 and Timer4 (if available) are used as clock sources as PWM modules

T3CON<6,3>=01

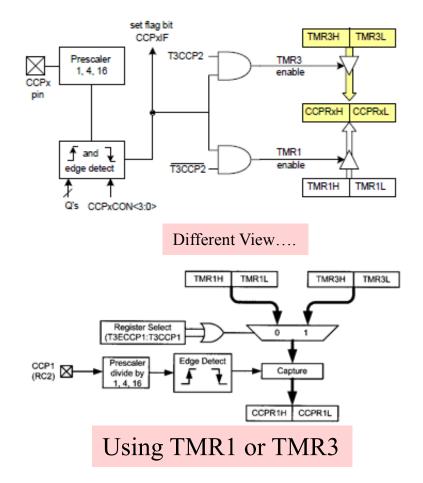

#### Capture Mode

### CCP in the Capture Mode (1 of 2)

#### □ When do events arrive?

- Physical time represented by the count value in a counter

- An event is represented by a signal edge

- Main use of CCP is to capture event arrival time by latching in the count value when the signal arrives

- □ The PIC18 event can be one of the following

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

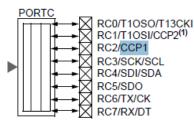

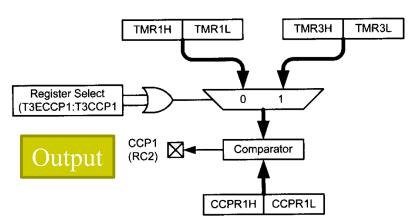

- □ CCPR1 register captures the 16-bit value of Timer1 (or Timer3) when an event occurs on pin RC2/CCP1.

- □ When a capture occurs, the interrupt request flag bit CCP1IF (Bit2 in PIR1) is set and must be cleared for the next operation.

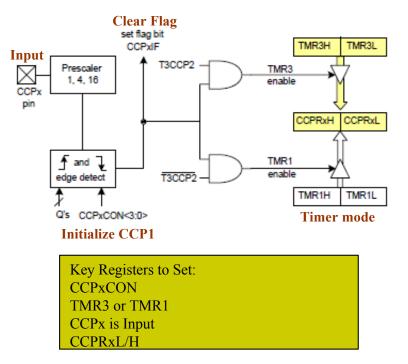

#### CCP in the Capture Mode (2 of 2)

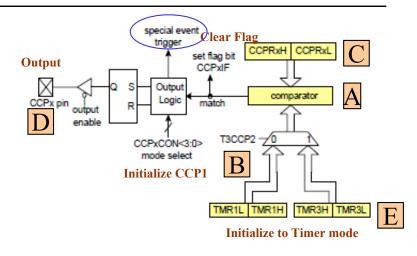

#### □ To capture an event:

- Set up pin RC2/CCP1 of PORTC as the input.

- Initialize Timer1 in the timer mode or synchronized counter mode by writing to T1CON/ T3CON register.

- □ Asynch mode does not work

- Initialize CCP1 by writing to the CCP1CON register.

- Clear the CCP1IF flag to continue the next operation when a capture occurs.

- Clear CCP1IE and CCP1IF to avoid a false interrupt when capture mode is changed.

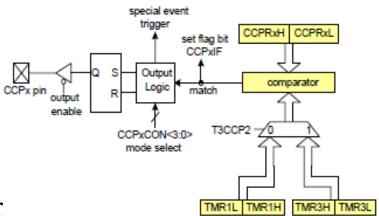

### Compare Mode

### CCP in the Compare Mode (1 of 2)

- □ CCP compare applications

- Generation of a single pulse, a train of pulses, periodic waveform with certain duty cycle, specified time delay

- 16-bit value loaded by the user in CCPR1 (or CCPRx) is constantly compared with the TMR1 (or TMR3) register when the timers are running in either timer mode or synchronized counter mode.

- □ When a **match** occurs, the pin RC2/CCP1 on PORTC is driven high, low, or toggled based on mode select bits in the CCP1CO (Bit3-Bit0 in CCP1 control register), and the interrupt flag bit CCP1IF is set.

### CCP in the Compare Mode (2 of 2)

- □ To set up CCP1 in the Compare mode:

- Set up pin RC2/CCP1 of PORTC as output.

- Initialize Timer1 in the timer mode or the synchronized counter mode by writing to the T1CON/ T3CON register.

- Initialize CCP1 by writing to the CCP1CON register.

- Clear the flag CCP1IF, which is set when a compare occurs, and must be cleared to continue to the next operation.

- For a special event trigger, an internal hardware trigger is generated that can be used to initiate an action.

- The special event trigger output resets Timer1.

## Example

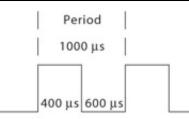

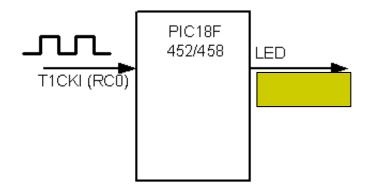

Measure the period of the input clock

1- Assume the clock is coming from RC2 → CCP1

3- Use TMR1

```

void main (void)

OSCCON = 0 \times 70;

OSCTUNEbits.PLLEN = 1; // x4 PLL enabled = 32MHz

CCP1CON = 0 \times 05;

T3CON = 0 \times 00;

T1CON = 0 \times 0;

TRISD = 0 \times 0;

TRISCbits.TRISC2 = 1; // Set RC2 // Make sure the input

CCPR1L = 0;

CCPR1H = 0;

while(1)

TMR1H = 0;

TMR1L = 0;

PIR1bits.CCP1IF=0;

PORTDbits.RD0=~PORTDbits.RD0;

```

while(PIR1bits.CCP1IF==0); // Wait for the first rising edge

T1CONbits.TMR1ON=1;

PIR1bits.CCP1IF=0;

while(PIR1bits.CCP1IF==0); // wait for the second rising edge

T1CONbits.TMR1ON=0;

PulsePeriod[0]=CCPR1L; // the number of counts are here!

PulsePeriod[1]=CCPR1H;

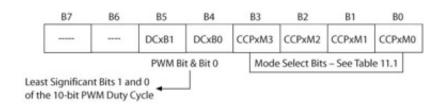

#### Pulse Width Modulation

| Bas                       | ic Ide                    | a Reg                                      |            | B5<br>DCxB1                          | B4<br>DCxB0<br>it & Bit 0 | B3<br>CCPxM3<br>Mode | B2<br>CCPxM2<br>Select Bits | B1<br>CCPxM1<br>5 – See Tabl | B0<br>CCPxM0<br>e 11.1 |

|---------------------------|---------------------------|--------------------------------------------|------------|--------------------------------------|---------------------------|----------------------|-----------------------------|------------------------------|------------------------|

| DC1B2<br>0<br>0<br>1<br>1 | DC1B1<br>0<br>1<br>0<br>1 | Decimal points<br>0<br>0.25<br>0.5<br>0.75 | 50%<br>75% | 6 DC _<br>6 DC _<br>6 DC _<br>8 DC _ |                           |                      | ·                           |                              |                        |

For example 75% of COUNT (e.g. Pry=249) = 186.75  $\rightarrow$  0.75 is equivalent to **DC1B1 & DC1B0 = 11**

# CCP in the Pulse Width Modulation (PWM) Mode (0 of 3)

- □ CCPx pin can output a 10-bit resolution periodic digital waveform with programmable duty cycle

- Duty cycle to be generated is a 10-bit value

- Upper 8-bits stored in CCPRxH register

- Lower 2-bits stored in bit 5 and bit 4 of

- □ CCPxCON register Duty cycle value compared with TMRy cascaded with 2-bit clock in every instruction cycle

- When values are equal, CCPx pin pulled low

- TMRy register compared to PRy register in every clock cycle, when equal following events occur on next increment cycle

- CCPx pin pulled high

- TMRy register cleared

- PWM duty cycle is latched from CCPRxl into CCPRxH

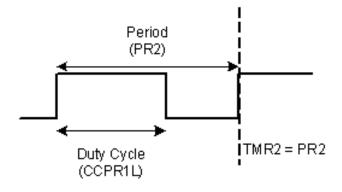

#### CCP in the Pulse Width Modulation (PWM) Mode (1 of 3)

- A CCP module in conjunction with Timer2 can be set up to output a pulse wave form for a given frequency and a duty cycle.

- □ The CCP module uses a 10-bit number to specify the duty cycle.

- □ The 8-bit number loaded into the PR2 register specify the PWM period.

- PWM period and duty cycle can be calculated using the following

PWM period = [(PRy) + 1] × 4 × T<sub>osc</sub> × (TMRy prescale factor)

(in sec) **PWM duty cycle** = (CCPRxL:CCPxCON<5:4>) × T<sub>osc</sub> × (TMRy prescale factor) or CCPR1L = [PR2+1]\*DutyCycle Time unit = crystal oscillator cycle

### CCP in the PWM Mode (2 of 3)

- When TMR2 is equal to PR2, the following three events occur in the next increment cycle:

- TMR2 is cleared.

- Pin RC2/CCP1 of PORTC is set high.

- The PWM duty-cycle byte is latched from CCPR1L into CCPR1H.

- When CCPR1H and TMR2 match again for the specified duty cycle, the CCP1 pin is cleared.

#### CCP in the PWM Mode (3 of 3)

- □ To Initialize CCP1 in the PWM mode:

- Set up pin RC2/CCP1 of PORTC as output.

- Set up PWM period by writing to the PR2 register.

- Set up PWM duty cycle by writing to CCPR1L register and Bit5-Bit4 of CCP1CON register.

- Set up TMR2 prescale value and Timer2 in timer mode by writing to T2CON register.

- Enable CCP1 module in the PWM mode.

- Set up CCP1 by writing to the CCP1CON register.

#### Example of Register Setting for PWM

- Configure CCP1 in PWM mode to generate a digital waveform with 40% duty cycle and 10 KHz frequency assuming that the PIC18 MCU is running with a 32 MHz crystal oscillator. Assuming prescale=4 for timer 2.

- □ Timer setting

- Use Timer2 as the base timer of CCP1 for PWM mode

- Set Prescaler to Timer2 to 1:4

- Period register value: PR2 = 32MHz / [4x4x10KHz] 1 = 199

- □ PR2 = Fosc /[4xNxFdesired]-1 ; N is the prescaler value

- Duty Cycle Value: CCPR1L = [PR2+1]\*DutyCycle

- $= 200 \times 40\% = 80.00$

| _ | B7              | B6 | B5    | B4    |        | B3 | B2          | B1         | BO     |  |

|---|-----------------|----|-------|-------|--------|----|-------------|------------|--------|--|

|   |                 |    | DCxB1 | DCxB0 | CCPxM3 |    | CCPxM2      | CCPxM1     | CCPxM0 |  |

|   | PWM Bit & Bit 0 |    |       |       |        |    | Select Bits | - See Tabl | e 11.1 |  |

|   | DCxB0 & B1 = 00 |    |       |       |        |    |             |            |        |  |

#### 99 (x = 1, ..., 3) (x

#### CCPRL Register= 80d

PR2 Register = 199d

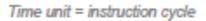

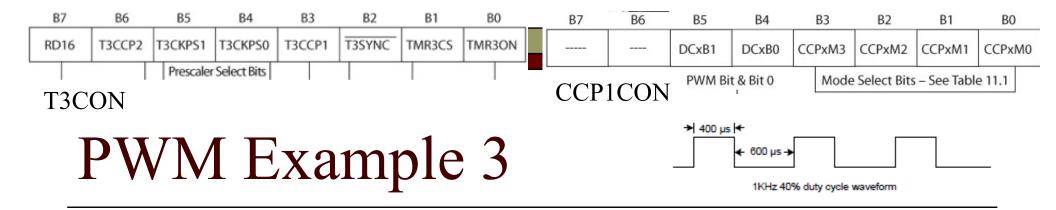

□ Use CCP1 to generate a periodic waveform with 40% duty cycle and 1 KHz frequency assuming that the instruction cycle clock - use timer3 as the base timer, set prescale = 1, assume high priority. Assume 4MHz crystal oscillator.

#### Programing ECCP (CCP1) In PIC18F46K20 - 1

Write a program that measures the period of the incoming signal; at RC2 (CCP1) – This is the ECCP in 44-pin TQFP 46K20 RC7/RX/DT ----RD4/PSP4 ++ 32 - RC0/T10S0/T13CKI 31 - OSC2/CLKOUT/RA6 ► IT RD5/PSP5/P1B PIC18F43K20 OSC1/CLKIN/RA7 RD6/PSP6/P1C Vee RD7/PSP7/P1D ►HH PIC18F44K20 VDD • I I I I PIC18F45K20 - HH RE2/CS/AN7 Mon. PIC18F46K20 RE1/WR/AN6 RB0/INT0/FLT0/AN12 ++ RB1/INT1/AN10/C12IN3- ---25 - RE0/RD/AN5 RB2/INT2/ANB +++ CTT RB3/AN9/C12IN2-/CCP2<sup>(1)</sup> ++ CTT 24 RA5/AN4/SS/HLVDIN/C2OUT

```

void main (void)

```

```

//** Clock Selection ****

// IRCFx = 100 // 2 MHz clock --> 2usec

//OSCCON = 0x40;

//OSCTUNEbits.PLLEN = 0; // x4 PLL disabled

OSCCON = Ox70;

// IRCFx = 111 (8 MHz) or --> 0.125 used

OSCTUNEbits.PLLEN = 1;

// x4 PLL enabled = 32MHz

// *** Initializing the CCPl (ECCP)

CCP1CON = 0 \times 05; s

T3CON = O \times OO :

T1CON = O \times O =

TRISD = 0 \times 0;

TRISCbits.TRISC2 = 1; // Set RC2 // Make sure the input

// is a square signal with no offset.

CCPRLL = 0;

CCPR1H = 0;

while(1)

\mathbf{TMR1H} = \mathbf{0}

TMR1L = 0:

PIRIbits.CCP1IF=0;

PORTDbits.RDO=~PORTDbits.RDO;

while (PIRIbits.CCP1IF==0); // Wait for the first rising edge

T1CONbits.TMR10N=1:

PIRIbits.CCP1IF=0;

while (PIR1bits.CCP11F==0); // wait for the second rising edge

T1CONbits.TMR10N=0;

PulsePeriod[0]=CCPR1L; // the number of counts are here!

PulsePeriod[1]=CCPR1H;

```

#### Programing ECCP (CCP1) In PIC18F46K20 - 2

#### Example of PWM using CCP1(RC2)

|                         | // main program                                                                                                                                     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | void main (void)                                                                                                                                    |

|                         | <pre>{ OSCCON = 0x40; // IRCFx = 100 // 2 MHz clock&gt; 2usec OSCTUNEbits.PLLEN = 0; // x4 PLL disabled</pre>                                       |

| Note that we use        | OSCIONEDICS.FLLEN - 0, // X4 FLL disabled                                                                                                           |

| OSCTUNE to adjust       | TRISC = OxFB;                                                                                                                                       |

| The frequency           | TRISD = $0 \times 00$ ;<br>CCP1CON = $0 \times 3C$ ; $101*4*4*0.5usec = 808 usec = Period$                                                          |

|                         | PR2=100; // Note: refer to section 11.4.1 or datasheet.                                                                                             |

| CCPR1L sets the         | T2CON=0x01;<br>OSCTUNE = Ob00010011; // this is to adjust the period of the pulses                                                                  |

| value of the duty cycle | while(1)                                                                                                                                            |

|                         | {     // For CCPR1L=25; the period is 8822 usec; DC= 223 usec     CCPR1L = 50; //Can be 25 or 50% duty cycle     TMR2=0x0;     DID14 is = TWD2IR=0; |

|                         | PIRIbits.TMR2IF=0;<br>T2COURT - TWR2OU-1;                                                                                                           |

|                         | T2CONbits.TMR2ON=1;<br>//PORTDbits.RDO = ~PORTDbits.RDO;                                                                                            |

|                         | <pre>while (PIR1bits.TMR2IF==0);</pre>                                                                                                              |

|                         | PORTDbits.RDO = ~PORTDbits.RDO;                                                                                                                     |

|                         | CCPR1L. < DC1B2:DC1B1 >= PR2*DC%                                                                                                                    |

$50.00 = 100 * 0.5 \rightarrow$  for 50% Duty Cycle

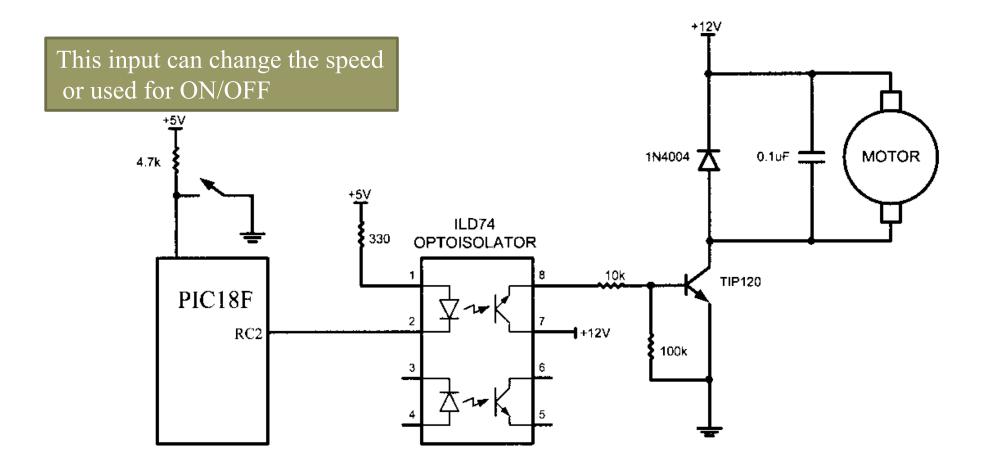

#### Controlling a DC Motor Using PWM