# Chapter 10

Basic Concepts in Interrupts

□An interrupt is a communication process set up in a microprocessor or microcontroller in which:

- An internal or external device requests the MPU to stop the processing

- The MPU acknowledges the request

- Attends to the request

- □Goes back to processing where it was interrupted

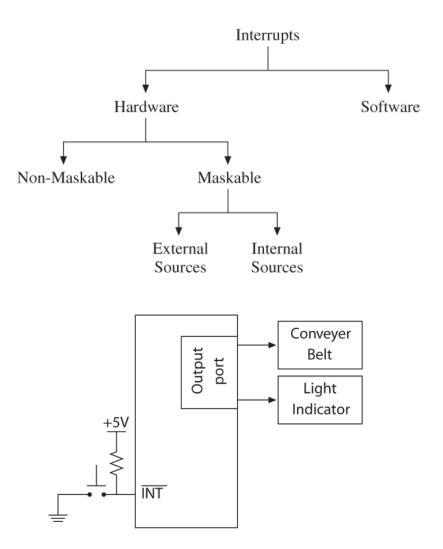

## Types of Interrupts

#### □Hardware interrupts

Maskable: can be masked or disabled

□Two groups: external and internal interrupts

External through designated I/O pins

■ Internal by Timers, A/D, etc.

■Non-maskable: cannot be disabled

- □Software interrupts: generally used when the situation requires stop processing and start all over

- Examples: divide by zero or stack overflow

- Generally, microcontrollers do not include software interrupts

#### MPU Response to Interrupts (1 of 2)

□When the interrupt process is enabled, the MPU, during execution, checks the interrupt request flag just before the end of each instruction.

□If the interrupt request is present, the MPU:

**Completes** the execution of the instruction

- Resets the interrupt flag

- Saves the address of the program counter on the stack

- □Some interrupt processes also save contents of MPU registers on the stack.

Stops the execution

#### MPU Response to Interrupts (2 of 2)

□To restart the execution, the MPU needs to be redirected to the memory location where the interrupt request can be met.

Accomplished by interrupt vectors

□The set of instructions written to meet the request (or to accomplish the task) is called an interrupt service routine (ISR).

Once the request is accomplished, the MPU should find its way back to the instruction, next memory location where it was interrupted.

Accomplished by a specific return instruction

```

Main code

Setup interrupt vectors

HERE: GOTO HERE

ORG 0x100

INT1_ISR: ISR code

.....

A 4 4 4

RFTFIF

END

```

## Interrupt Service Routine (ISR)

#### Main code **CINENTIAL** RETFIE instruction format ■RETFIE [s] ;Return from interrupt: s = Setup interrupt vectors 0 or 1 HERE: GOTO HERE $\Box$ If s =1, the MPU also retrieves the contents of W, BSR, and STATUS register (previously saved) before enabling the global interrupt bit. **ORG 0x100** ■Format: RETFIE FAST INT1\_ISR: ISR code The same as RETFIE 1 except the formats ..... are different $\mathbf{x} \in \mathbf{x} \in \mathbf{R}$ RETFIE END

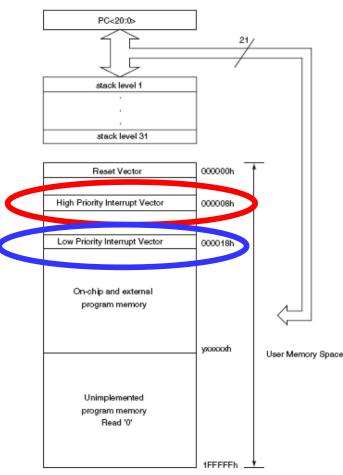

#### Interrupt Vectors

Direct the MPU to the location where the interrupt request is accomplished.

They are:

- Defined memory location where a specific memory location/s is assigned to the interrupt request

- Defined vector location where specific memory locations assigned to store the vector addresses of the ISRs

- Specified by external hardware: The interrupt vector address (or a part of it) is provided through external hardware using an interrupt acknowledge signal.

Note. y can be 0 or 1 whereas x can be 0-F

#### Interrupt Service Routine (ISR)

□A group of instructions that accomplishes the task requested by the interrupting source

- □Similar to a subroutine except that the ISR must be terminated in a Return instruction specially designed for interrupts

- The Return instruction, when executed, finds the return address on the stack and redirects the program execution where the program was interrupted.

- ■Some Return instructions are designed to retrieve the contents of MPU registers if saved as a part of the interrupts.

- ■→RETFIE FAST (1/0)

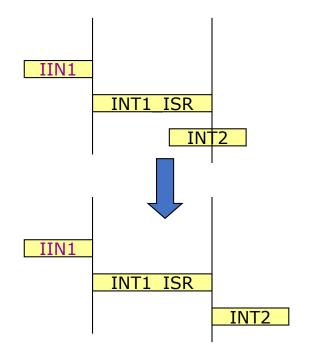

#### **Interrupt Priorities**

□Rationale for priorities

Multiple interrupt sources exist in a system, and more than one interrupt requests can arrive simultaneously.

Example: A/D and Timer0

- When one request is being served (meaning when the MPU is executing an ISR), another request can arrive.

- $\blacksquare \rightarrow$  the interrupt requests must be prioritized.

- Most MCUs (and MPUs) include an interrupt priority scheme. Some are based on hardware and some use software.

**INT1** has higher priority than **INT2**

#### Reset as a Special Purpose Interrupt

Reset is an external signal that enables the processor to begin execution or interrupts the processor if the processor is executing instructions.

- □There are at least two types of resets in microcontrollerbased systems.

- Power-on reset and manual reset

□When the reset signal is activated, it establishes or reestablishes the initial conditions of the processor and directs the processor to a specific starting memory location.

#### PIC18 Interrupts

#### □PIC18 Microcontroller family

■Has multiple sources that can send interrupt requests

□Does not have any non-maskable or software interrupts; all interrupts are maskable (can be disabled)

#### Has a priority scheme divided into two groups

□High priority and low priority

Uses many Special Function Registers (SFRs) to implement the interrupt process

- Divided into two groups

- External sources and internal peripheral sources on the MCU chip

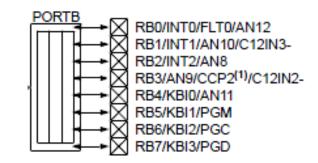

- External sources

- Three pins of PORTB -RB0/INTO, RB1/INT1, and RB2/INT2 (edge driven)

- Change in logic levels of pins RB4-RB7 of PORTB can be recognized as interrupts

- Internal sources

- Use SFRs to setup the interrupt process....

□Internal peripheral sources

Examples: Timers, A/D Converter, Serial I/O, and Low-Voltage Detection Module

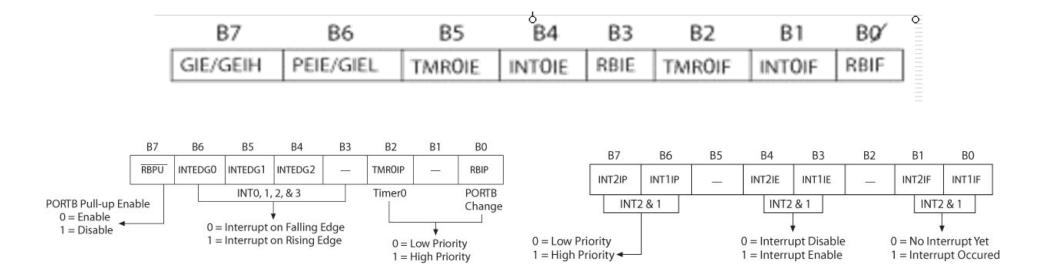

**□**SFRs

■Used to setup the interrupt process:

RCON Register Control (global priority)

INTCON Interrupt Control

INTCON2Interrupt Control2

INTCON3 Interrupt Control3

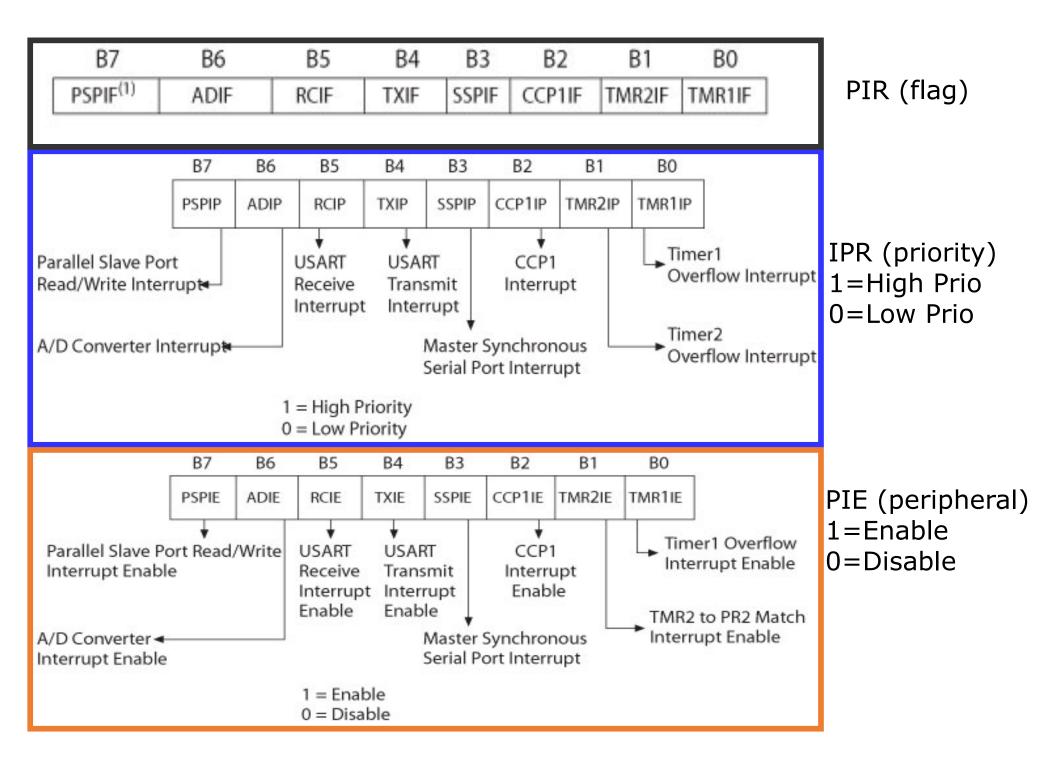

PIR1 and PIR2 Peripheral Interrupt Register 1 & 2

PIE1 and PIE2 Peripheral Interrupt Enable 1 & 2

IPR1 and IPR2 Interrupt Priority Register 1 & 2

#### **Click here: Summery of Interrupt Registers**

□To recognize the occurrence of an interrupt request, the MPU needs to check the following three bits:

The flag bit to indicate that an interrupt request is present

The enable bit to redirect the program execution to the interrupt vector address

The priority bit (if set) to select priority

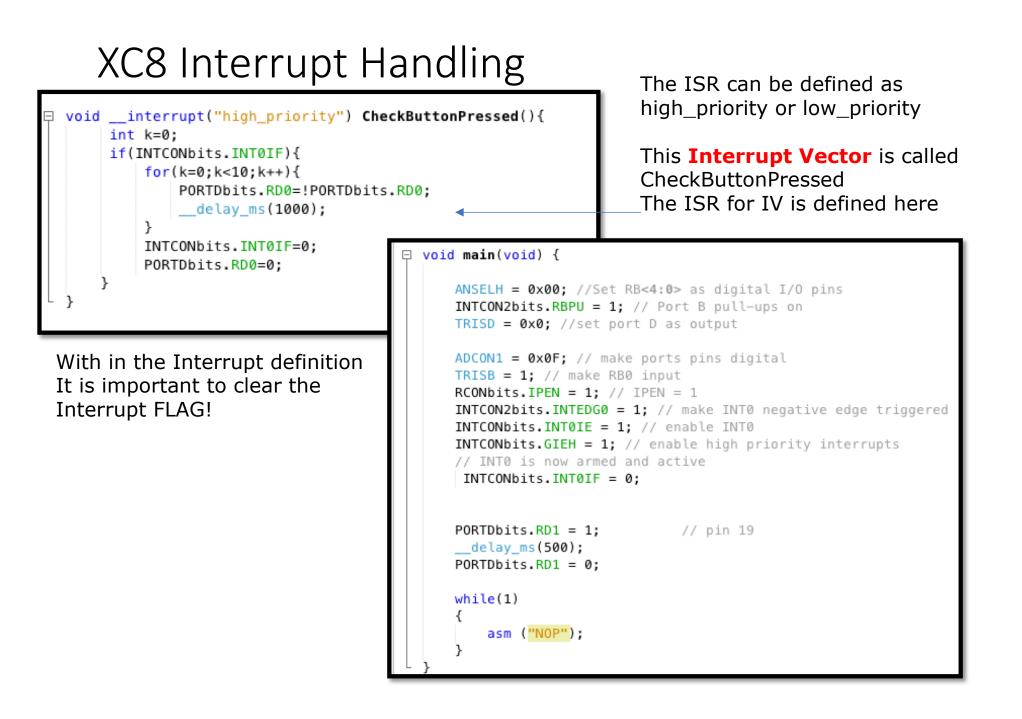

□In PIC interrupt are controlled by three bits in three different registers.

- The IE bit is the interrupt enable bit used to enable the interrupt.

- The IP bit is the interrupt priority bit which selects the priority (high or low).

- The IF bit is the interrupt flag that indicates the interrupt has occurs. This bit must be cleared in the interrupt service function or no future interrupt will ever take effect.

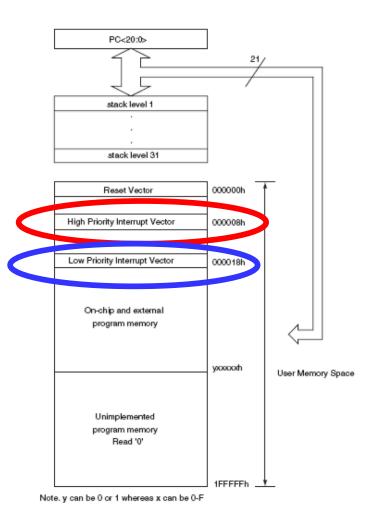

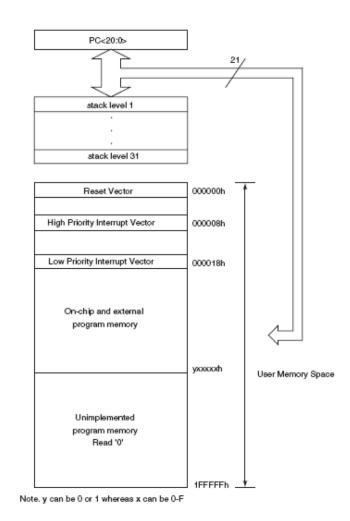

#### Interrupt Priorities and RCON Register (1 of 2)

□Any interrupt can be set up as highpriority or low-priority.

- ■All high-priority interrupts are directed to the interrupt vector location 000008H.

- ■All low-priority interrupts are directed to the interrupt vector location 000018H.

- A high-priority interrupt can interrupt a low-priority interrupt in progress.

#### Interrupt Priorities and RCON Register (2 of 2)

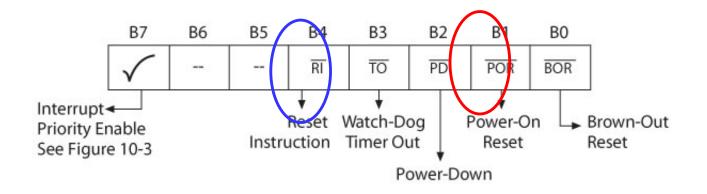

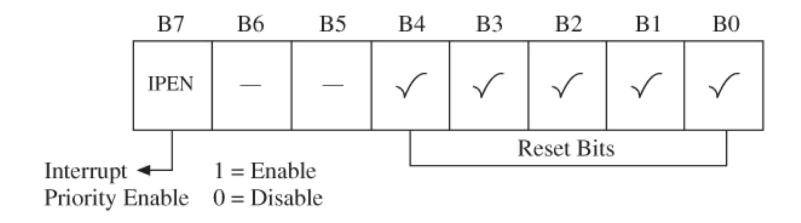

□The interrupt priority feature is enabled by Bit7 (IPEN) in RCON register.

# External Interrupts and INTCON Registers (1 of 3)

□Three registers with interrupt bit specifications primarily for external interrupt sources. INTCON (3)

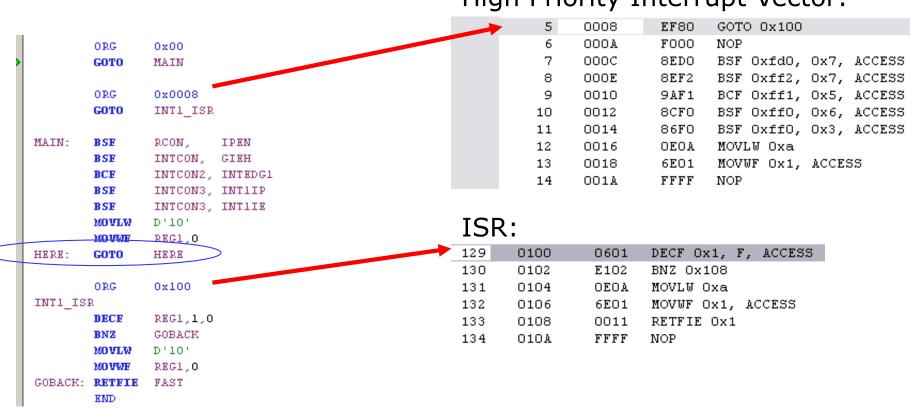

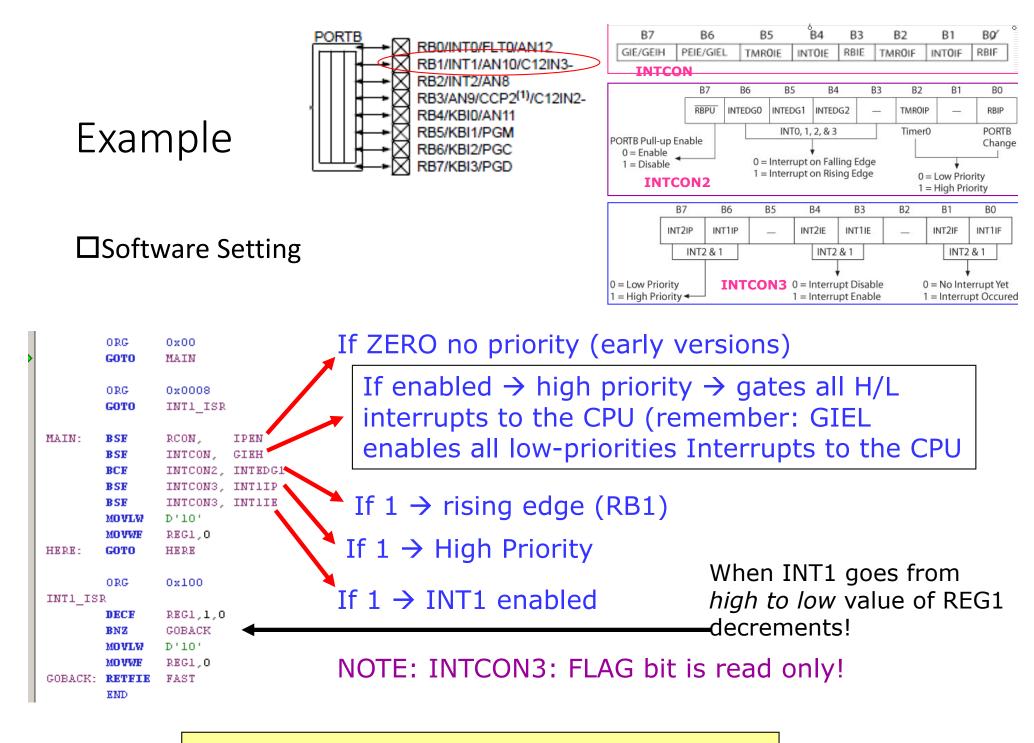

#### Example

$\Box$ Write an instruction to setup INT1 as the high priority interrupt. (INT1  $\rightarrow$  RB1)

High Priority Interrupt Vector:

**Convert to C code!**

## Interrupt Setting (INTO high priority only)

| Name                     | Priority Bit   | Local Enable Bit | Local Flag Bit |

|--------------------------|----------------|------------------|----------------|

| INT0 external interrupt  | *              | INTCON,INT0IE    | INTCON,INT0IF  |

| INT1 external interrupt  | INTCON3,INT1IP | INTCON3,INT1IE   | INTCON3,INT1IF |

| INT2 external interrupt  | INTCON3,INT2IP | INTCON3,INT2IE   | INTCON3,INT2IF |

| RB port change interrupt | INTCON2,RBIP   | INTCON,RBIE      | INTCON,RBIF    |

| TMR0 overflow interrupt  | INTCON2,TMR0IP | INTCON,TMR0IE    | INTCON,TMR0IF  |

| TMR1 overflow interrupt  | IPR1,TMR1IP    | PIE1,TMR1IE      | PIR1,TMR1IF    |

| TMR3 overflow interrupt  | IPR2,TMR3IP    | PIE2,TMR3IE      | PIR2,TMR3IF    |

| TMR2 to match PR2 int.   | IPR1,TMR2IP    | PIE1,TMR2IE      | PIR1,TMR2IF    |

| CCP1 interrupt           | IPR1,CCP1IP    | PIE1,CCP1IE      | PIR1,CCP1IF    |

| CCP2 interrupt           | IPR2,CCP2IP    | PIE2,CCP2IE      | PIR2,CCP2IF    |

| A/D converter interrupt  | IPR1,ADIP      | PIE1,ADIE        | PIR1,ADIF      |

| USART receive interrupt  | IPR1,RCIP      | PIE1,RCIE        | PIR1,RCIF      |

| USART transmit interrupt | IPR1,TXIP      | PIE1,TXIE        | PIR1,TXIF      |

| Sync. serial port int.   | IPR1,SSPIP     | PIE1,SSPIE       | PIR1,SSPIF     |

| Parallel slave port int. | IPR1,PSPIP     | PIE1,PSPIE       | PIR1,PSPIF     |

| Low-voltage detect int.  | IPR2,LVDIP     | PIE2,LVDIE       | PIR2,LVDIF     |

| Bus-collision interrupt  | IPR2,BCLIP     | PIE2,BCLIE       | PIR2,BCLIF     |

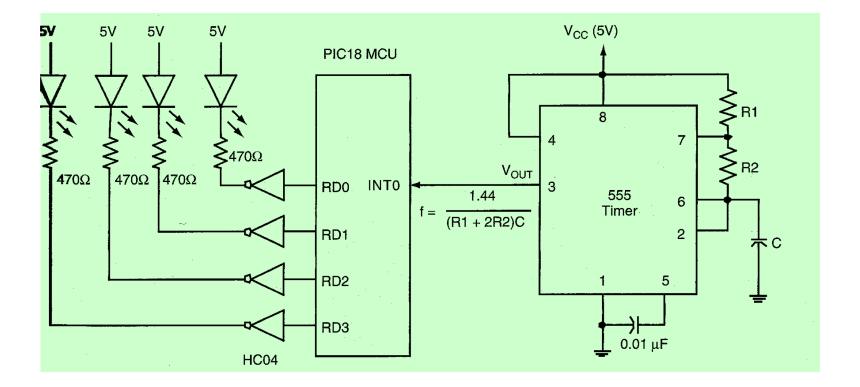

C Code Example

When a pulse is generated on INTO the high priority interrupt is generated!

| ADCON1 = 0x0F;                                                             | // make ports pins digital                                                                   |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| TRISB = 1;                                                                 | // make RB0 input                                                                            |

| RCONbits.IPEN = 1;                                                         | // IPEN = 1                                                                                  |

| INTCON2bits.INTEDG0 = 0;<br>INTCONbits.INT0IE = 1;<br>INTCONbits.GIEH = 1; | // make INT0 negative edge triggered<br>// enable INT0<br>// enable high priority interrupts |

// INT0 is now armed and active

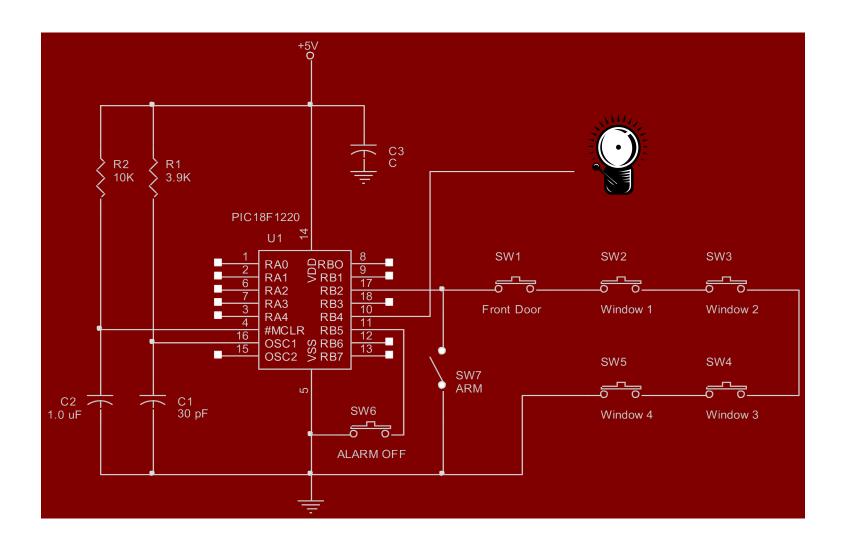

## C Code Example – Burglar Alarm Circuit

#### Another practical Example

Suppose you are given a circuit as shown below. Write a main program and an INT0 interrupt service routine in assembly language. The main program initializes a counter to 0, enables the INTO interrupt, and then stays in a while-loop to wait forever. The INTO interrupts service routine simply increments the counter by 1 and outputs it to the LEDs. Whenever is incremented to 15, the service routine resets it to 0. Choose appropriate component that the PIC1 8 receives an INTO interrupt roughly every second.

Handling Multiple Interrupt Sources

□In PIC18 MCU, all interrupt requests are directed to one of two memory locations:

000008H (high-priority) or 000018 (low-priority)

□When multiple requests are directed to these locations, the interrupt source must be identified by checking the interrupt flag through software instructions.

| IPR1 | PSPIP | ADIP | RCIP | TXIP | SSPIP | CCP1IP | TMR2IP | TMR1IP |

|------|-------|------|------|------|-------|--------|--------|--------|

| PIE1 | PSPIE | ADIE | RCIE | TXIE | SSPIE | CCP1IE | TMR2IE | TMR1IE |

## Example

| BSF<br>BSF<br>BCF<br>BSF | INTCON, GIEL<br>IPR1, TMR1IP<br>PIE1, TMR1IE<br>IPR1, TMR2IP<br>PIE1, TMR2IE | <pre>;Enable global low-priority - INTCON ,6&gt;<br/>;Set Timer1 as low-priority<br/>;Enable Timer1 overflow interrupt<br/>;Set Timer2 as low-priority<br/>;Enable Timer2 match interrupt</pre> |

|--------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCF                      | PIR1, TMR1IF                                                                 | ;Clear TMR1 flag                                                                                                                                                                                |

| CALL                     | TMR1L                                                                        | ;Call service subroutine                                                                                                                                                                        |

| BCF                      | PIR1,TMR2IF                                                                  | ;Clear TMR2 flag                                                                                                                                                                                |

| CALL                     | TMR2                                                                         | ;Call service subroutine                                                                                                                                                                        |

| Name                     | Priority Bit   | Local Enable Bit | Local Flag Bit |

|--------------------------|----------------|------------------|----------------|

| KB port enange interrupt | INTCOIN2, KDIF | INTCON, NDIE     | INTCON,RBIP    |

| TMR0 overflow interrupt  | INTCON2,TMR0IP | INTCON,TMR0IE    | INTCON,TMR0IF  |

| TMR1 overflow interrupt  | IPR1,TMR1IP    | PIE1,TMR11E      | PIR1,TMR11F    |

| TMR3 overflow interrupt  | IPR2,TMR3IP    | PIE2,TMR3IE      | PIR2,TMR3IF    |

| TMR2 to match PR2 int.   | IPR1,TMR2IP    | PIE1,TMR2IE      | PIR1,TMR2IF    |

#### Example of using multiple interrupts INT1=High Priority / TMR1 and TMR2 Low Priority

Assign the High Priority Interrupt Vector

Assign the Low Priority Interrupt Vector

Setup the interrupt registers for external interrupt

Setup the interrupt registers for internal interrupts

#### Example of using multiple interrupts INT1=High Priority / TMR1 and TMR2 Low Priority

|         |         |                |   |                 | > | 1      | 0000 | EF12 | GOTO 0x24                |

|---------|---------|----------------|---|-----------------|---|--------|------|------|--------------------------|

|         | 0.00    | 0x00           |   |                 |   | 2      | 0002 | F000 | NOP                      |

|         | ORG     |                |   |                 |   | 3      | 0004 | FFFF | NOP                      |

|         | GOTO    | MAIN           |   |                 |   | 4      | 0006 | FFFF | NOP                      |

|         |         |                | 2 |                 |   | 5      | 0008 | EF80 | GOTO 0x100               |

|         | ORG Ox( | 0008           |   |                 |   | 6      | 000A | F000 | NOP                      |

| INTCK:  |         |                | 5 | High priority   |   | 7      | 000C | FFFF | NOP                      |

|         | GOTO    | INT1_ISR       | ſ | <u> </u>        |   | 8      | 000E | FFFF | NOP                      |

|         |         | -              | J |                 |   | 9      | 0010 | FFFF | NOP                      |

|         | ORG Ox0 | 00018          | - |                 |   | 10     | 0012 | FFFF | NOP                      |

| TIMERCK |         |                | 7 |                 |   | 11     | 0014 | FFFF | NOP                      |

|         | BTFSC   | PIR1, TMR11F   |   | Low priority    |   | 12     | 0016 | FFFF | NOP                      |

|         |         |                | 7 | • •             |   | 13     | 0018 | BO9E | BTFSC Oxf9e, O, ACCESS   |

|         | GOTO    | TMR1_ISR       | [ | Two interrupts  |   | 14     | 001A | EF87 | GOTO Ox10e               |

|         | BTFSC   | PIR1, TMR2IF   | J | •               |   | 15     | 001C | F000 | NOP                      |

|         | GOTO    | TMR2_ISR       |   | Check Flag      |   | 16     | 001E | B29E | BTFSC Oxf9e, Ox1, ACCESS |

|         |         |                |   |                 |   | 17     | 0020 | EF91 | GOTO Ox122               |

| MAIN:   |         |                |   |                 |   | 18     | 0022 | F000 | NOP                      |

|         |         |                |   |                 |   | R.A. / |      | OE3F | MOVLW 0x3f               |

|         |         |                |   |                 |   |        | AIN  | 6E93 | MOVWF Oxf93, ACCESS      |

|         | BSF RC0 | ON, IPEN       | 7 |                 |   | 21     | 0028 | 8EDO | BSF OxfdO, Ox7, ACCESS   |

|         | BSF INT | ,              |   |                 |   | 22     | 002A | 8EF2 | BSF Oxff2, Ox7, ACCESS   |

|         |         | TCON2, INTEDGI | l | INT is speakled |   | 23     | 002C | 8AF1 | BSF Oxff1, Ox5, ACCESS   |

|         |         |                | 7 | INT is enabled  |   | 24     | 002E | 8CFO | BSF OxffO, Ox6, ACCESS   |

|         |         | TCON3, INTIIP  |   | Edge driven     |   | 25     | 0030 | 86FO | BSF OxffO, Ox3, ACCESS   |

|         | BSF IN: | TCON3, INTLIE  | J | Luge unven      |   | 26     | 0032 | 8CF2 | BSF Oxff2, Ox6, ACCESS   |

|         |         |                | 7 |                 |   | 27     | 0034 | 909F | BCF Oxf9f, O, ACCESS     |

|         | BSF IN: | TCON, GIEL     |   | INT is spekled  |   | 28     | 0036 | 809D | BSF Oxf9d, O, ACCESS     |

|         | BCF IPI | RI, TMRLIP     | l | INT is enabled  |   | 29     | 0038 | 929F | BCF Oxf9f, Ox1, ACCESS   |

|         | BSE PII | EL, TMRLIE     | 7 | Edge driven     |   | 30     | 003A | 829D | BSF Oxf9d, Ox1, ACCESS   |

|         |         | RI, TMR2IP     |   | Luye unven      |   | 31     | 003C | OEOA | MOVLW Oxa                |

|         |         | EL, TMR2IE     | J |                 |   | 32     | 003E | 6E01 | MOVWF 0x1, ACCESS        |

|         |         |                |   |                 |   | 33     | 0040 | EF2O | GOTO 0x40                |

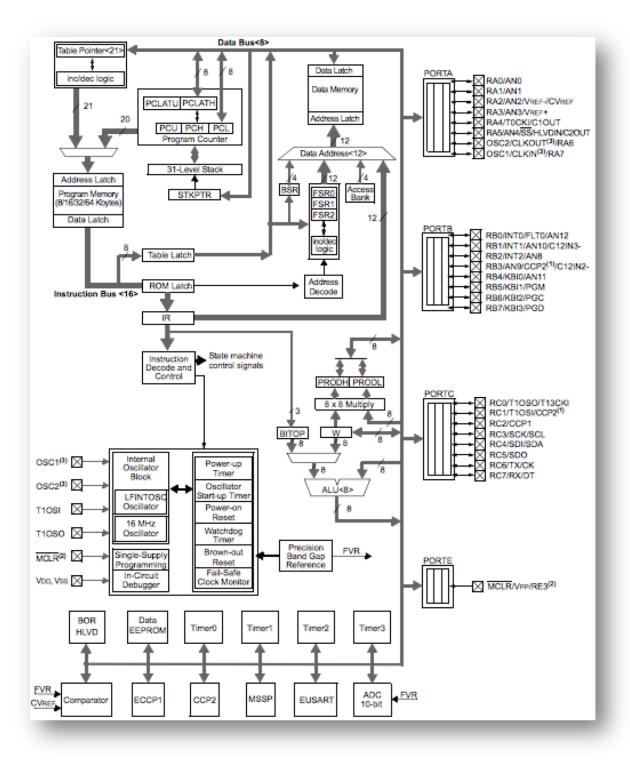

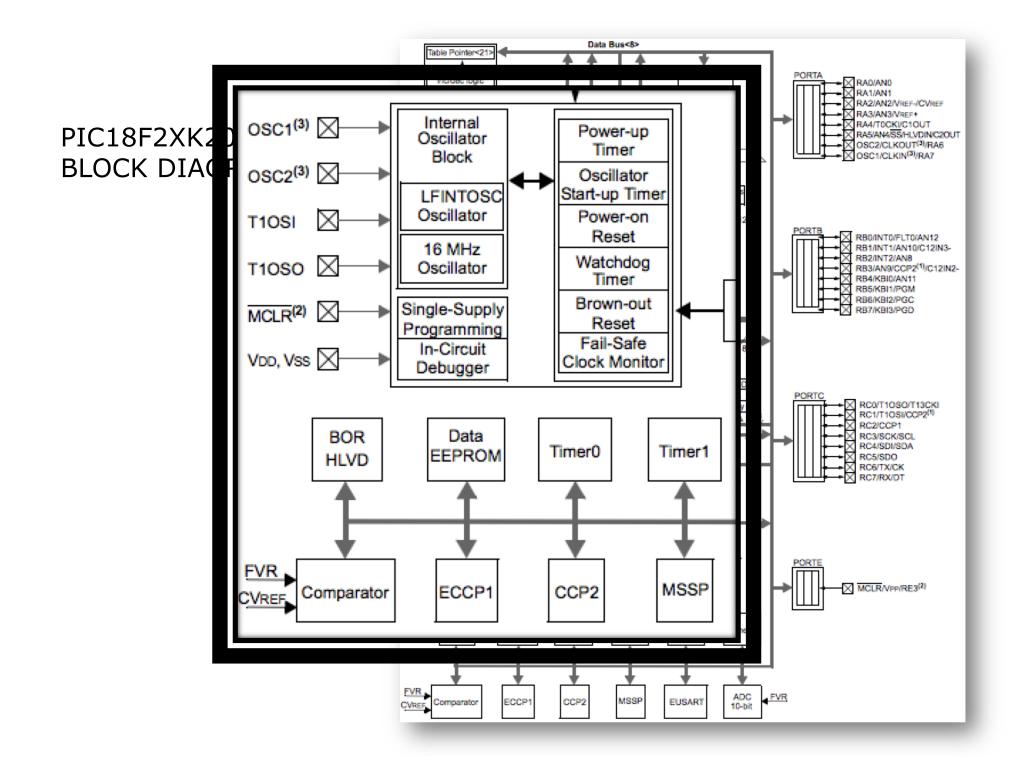

#### PIC18F2XK20 (28-PIN) BLOCK DIAGRAM

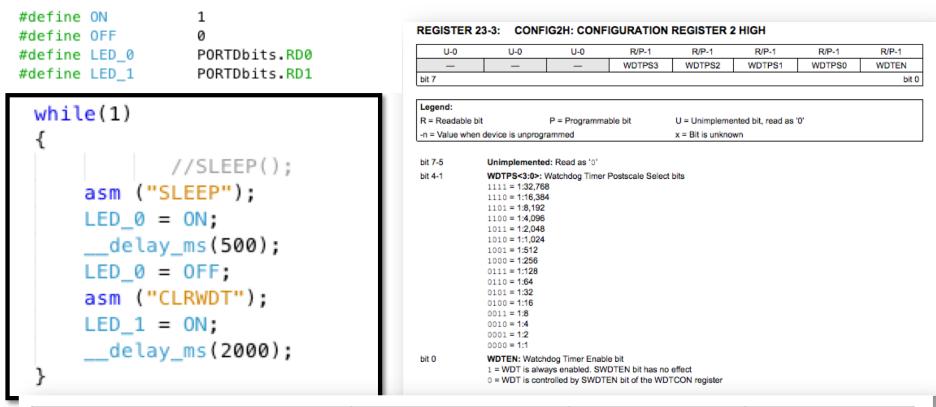

# SLEEP and WDT

The SLEEP mode can reduce the power! The CLRWDT is used to reset the WDT Refer to the SPEC sheet.

| C statement                  | Assembly Language | Scaling factor | Time to Reset |  |

|------------------------------|-------------------|----------------|---------------|--|

| #pragma config WDTPS = 1     | _WDTPS_1_2H       | 1:1            | 4 ms          |  |

| #pragma config WDTPS = 32768 | _WDTPS_32768_2H   | 1:32768        | 131.072 sec   |  |

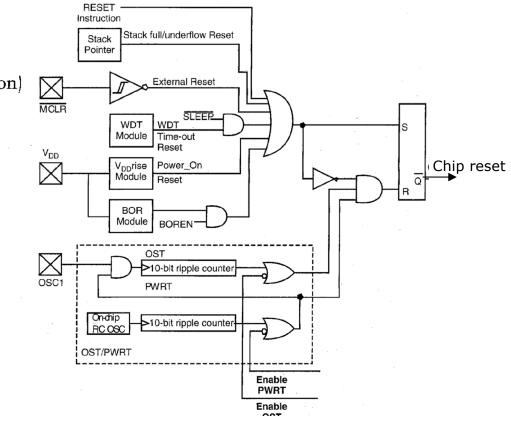

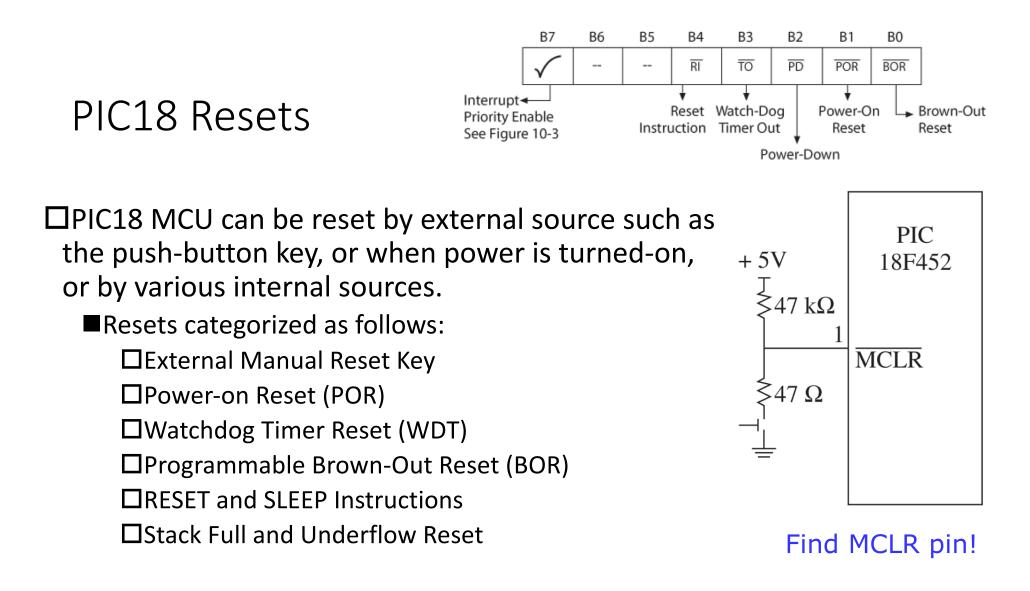

#### PIC18 Resets

□When the reset signal is activated:

- The MPU goes into a reset state during which the initial conditions are established.

- ■The program counter is cleared to 000000 which is called the reset vector.

- ■The MPU begins the execution of instructions from location 000000.

#### On Chip reset circuit for PIC18

- Power-on reset (POR)

- MCLR pin reset during normal operation

- MCLR pin reset during SLEEP

- Watchdog timer (WDT) reset (during normal operation)

- Programmable brown-out reset (BOR)

- RESET instruction

- Stack full reset

- Stack underflow reset

### Example of Reset Programming

- Identifying a power-on reset

- IF\_ RCON,NOT\_POR == 0 ;POR has occurred

- setf RCON ;Reinitialize all reset flags after power on

- <take action particular to power—on reset>

- ENDIF\_

- Identifying a reset due to execution of a "reset" instruction

- IF\_RCON,NOT\_RI == 0 ;reset' instruction has been executed

- bsf RCON.NOT\_RI ;Set bit to distinguish froe other resets

- <take appropriate action in response to "reset" instruction>

- ENDIF