## MICROCONTROLLER THEORY AND APPLICATIONS WITH THE PIC18F

### M. RAFIQUZZAMAN

### **Microcontroller Theory**

and Applications with the PIC18F

## Microcontroller Theory and Applications with the PIC18F

**First Edition**

#### M. RAFIQUZZAMAN, Ph.D.

Professor California State Polytechnic University, Pomona and President Rafi Systems, Inc. Diamond Bar, California

| Vice President and Executive Publisher | Don Fowley          |

|----------------------------------------|---------------------|

| Associate Publisher                    | Daniel Sayre        |

| Marketing Manager                      | Chris Ruel          |

| Production Manager                     | Micheline Frederick |

| Cover Designer                         | Wendy Lai           |

| Editorial Assistant                    | Katie Singleton     |

Copyright © 2011 by John Wiley & Sons, Inc. All rights reserved.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

This title was set by the author and printed and bound by Hamilton Printing.

Founded in 1807, John Wiley & Sons, Inc. has been a valued source of knowledge and understanding for more than 200 years, helping people around the world meet their needs and fulfill their aspirations. Our company is built on a foundation of principles that include responsibility to the communities we serve and where we live and work. In 2008, we launched a Corporate Citizenship Initiative, a global effort to address the environmental, social, economic, and ethical challenges we face in our business. Among the issues we are addressing are carbon impact, paper specifications and procurement, ethical conduct within our business and among our vendors, and community and charitable support. For more information, please visit our website: www.wiley. com/go/citizenship.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 646-8600, or on the Web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permission.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representation or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor the author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

"Evaluation copies are provided to qualified academics and professionals for review purposes only, for use in their courses during the next academic year. These copies are licensed and may not be sold or transferred to a third party. Upon completion of the review period, please return the evaluation copy to Wiley. Return instructions and a free of charge return shipping label are available at www.wiley.com/go/returnlabel. Outside of the United States, please contact your local representative."

#### Library of Congress Cataloging-in-Publication Data:

ISBN 13 978-0470-94769-2

Printed in the United States of America.

10 9 8 7 6 5 4 3 2 1

To my wife, Kusum; my son, Tito; and my brother, Elan

## Contents

| PREFAC     | CE X                                                                  | KIII     |

|------------|-----------------------------------------------------------------------|----------|

| CREDIT     | rs x                                                                  | VII      |

| 1. INTR    | ODUCTION TO MICROCONTROLLERS                                          | 1        |

| 1.1        | Explanation of Terms                                                  | 2        |

| 1.2        | Microcontroller Data Types                                            | 6        |

|            | 1.2.1 Unsigned and Signed Binary Numbers                              | 6        |

|            | 1.2.2 ASCII and EBCDIC Codes                                          | 8        |

|            | 1.2.3 Unpacked and Packed Binary-Coded-Decimal Numbers                | 9        |

| 1.3        | Evolution of the Microcontroller                                      | 9        |

| 1.4        | Typical Microcontroller Applications                                  | 11       |

|            | 1.4.1 A Simple Microcontroller Application                            | 12       |

|            | 1.4.2 Embedded Controllers                                            | 12       |

| 2. MICF    | ROCONTROLLER BASICS                                                   | 15       |

| 2.1        | Basic Blocks of a Microcomputer                                       | 15       |

|            | 2.1.1 System Bus                                                      | 16       |

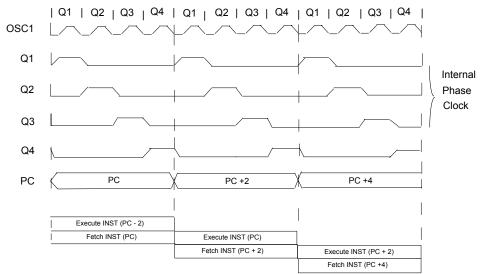

|            | 2.1.2 Clock Signals                                                   | 17       |

| 2.2        | Microcontroller Architectures                                         | 18       |

| 2.3        | Central Processing Unit (CPU)                                         | 19       |

|            | 2.3.1 Register Section                                                | 19       |

|            | 2.3.2 Control Unit                                                    | 26       |

|            | 2.3.3 Arithmetic and Logic Unit (ALU)                                 | 28       |

|            | 2.3.4 Simplified Explanation of Control Unit Design                   | 28       |

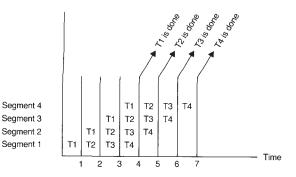

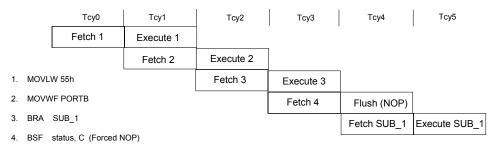

| 2.4        | Basic Concept of Pipelining                                           | 29       |

| 2.5        | RISC vs. CISC                                                         | 31       |

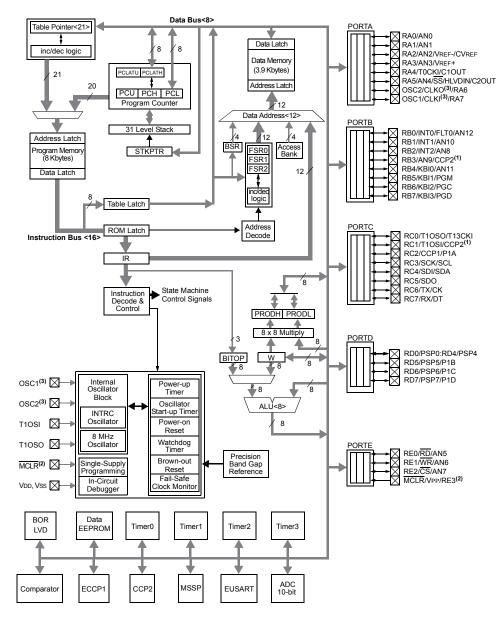

| 2.6        | Functional Representation of a Typical Microcontroller—The PIC18F4321 |          |

| ~          | stions and Problems                                                   | 34       |

| 3. INTR    | ODUCTION TO PROGRAMMING LANGUAGES                                     | 37       |

| 3.1        | Basics of Programming Languages                                       | 37       |

| 3.2        | Machine Language                                                      | 38       |

| 3.3        | Assembly Language                                                     | 38       |

|            | 3.3.1 Types of Assemblers                                             | 39       |

|            | 3.3.2 Assembler Delimiters                                            | 40       |

|            | 3.3.3 Specifying Numbers by Typical Assemblers                        | 41       |

|            | 3.3.4 Assembler Directives or Pseudoinstructions                      | 41       |

|            | 3.3.5 Assembly Language Instruction Formats                           | 43       |

|            | 3.3.6 Typical Instruction Set                                         | 45       |

|            | 3.3.7 Typical Addressing Modes                                        | 50       |

| 2.4        | 3.3.8 Subroutine Calls in Assembly Language                           | 52       |

| 3.4<br>3.5 | High-Level Language<br>Choosing a Programming Language                | 52<br>53 |

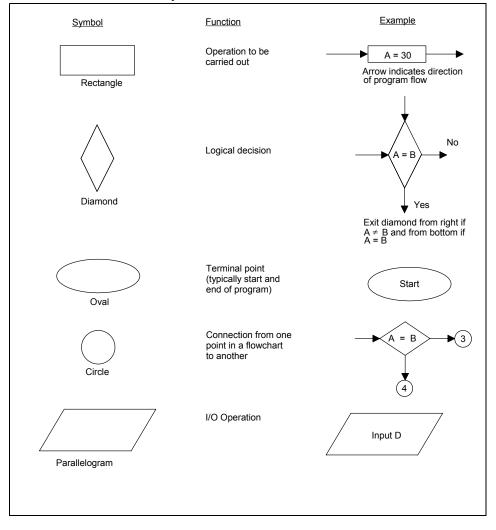

| 3.5        | Flowcharts                                                            | 53       |

|            | stions and Problems                                                   | 55<br>55 |

| Que        |                                                                       |          |

|            |                                                                       | vii      |

| <b>4</b> . N | <b>MICRO</b> | CONTROLLER MEMORY AND INPUT/OUTPUT (I/O)           | 57  |

|--------------|--------------|----------------------------------------------------|-----|

|              | 4.1          | Introduction to Microcontroller Memory             | 57  |

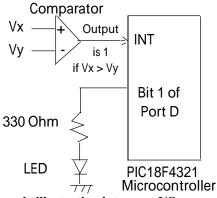

|              |              | 4.1.1 Main Memory                                  | 57  |

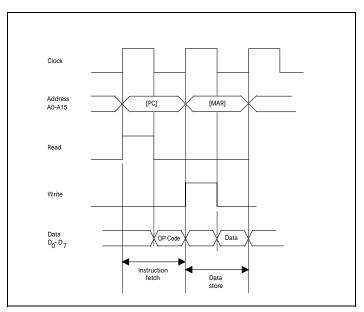

|              |              | 4.1.2 READ and WRITE Timing Diagrams               | 60  |

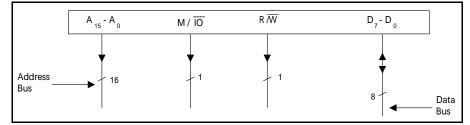

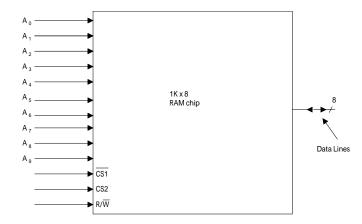

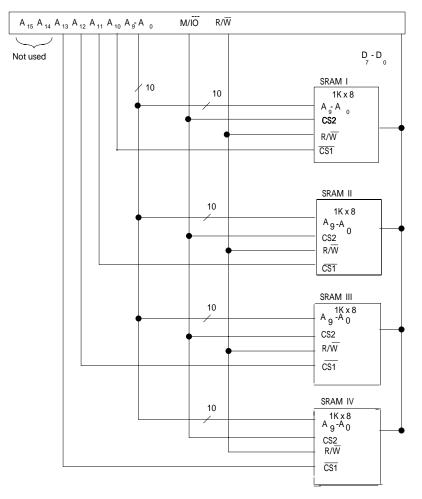

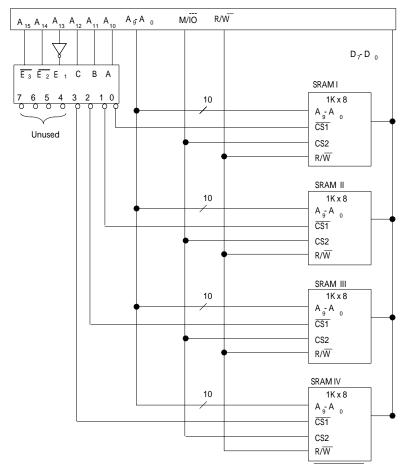

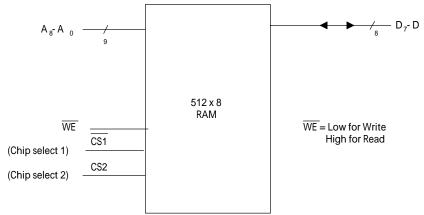

|              |              | 4.1.3 Main Memory Organization                     | 62  |

|              | 4.2          | Microcontroller Input/Output (I/O)                 | 66  |

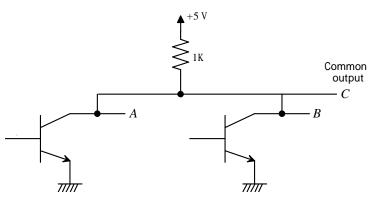

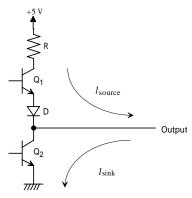

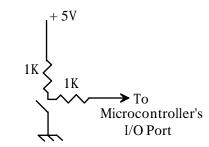

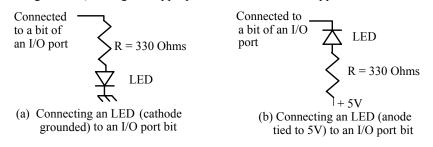

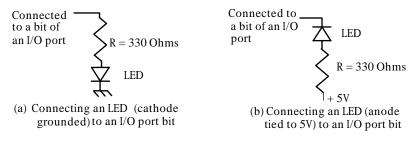

|              |              | 4.2.1 Overview of Digital Output Circuits          | 67  |

|              |              | 4.2.2 Simple I/O Devices                           | 69  |

|              |              | 4.2.3 Programmed I/O                               | 70  |

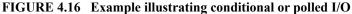

|              |              | 4.2.4 Unconditional and Conditional Programmed I/O | 72  |

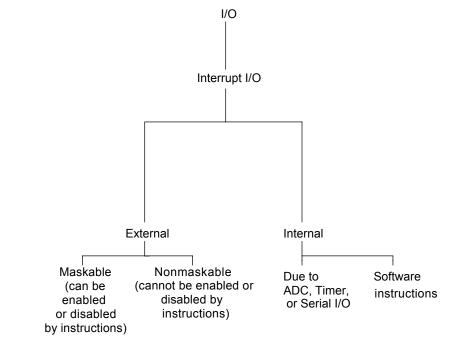

|              |              | 4.2.5 Interrupt I/O                                | 73  |

|              | Quest        | ons and Problems                                   | 77  |

| 5. I         | PIC18F       | ARCHITECTURE AND ADDRESSING MODES                  | 81  |

|              | 5.1          | Introduction                                       | 81  |

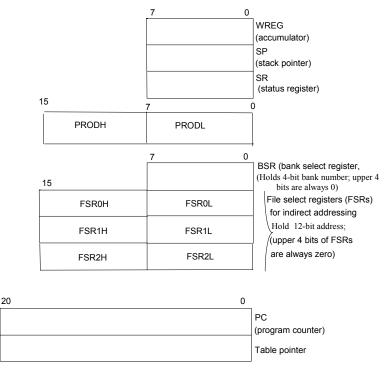

|              | 5.2          | PIC18F Register Architecture                       | 85  |

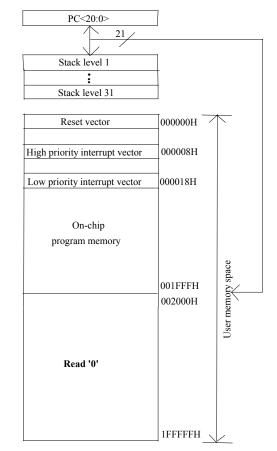

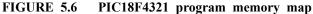

|              | 5.3          | PIC18F Memory Organization                         | 88  |

|              |              | 5.3.1 PIC18F Program Memory Map                    | 89  |

|              |              | 5.3.2 PIC18F Data Memory Map                       | 89  |

|              | 5.4          | PIC18F Addressing Modes                            | 91  |

|              |              | 5.4.1 Literal or Immediate Addressing Mode         | 92  |

|              |              | 5.4.2 Inherent or Implied Addressing Mode          | 92  |

|              |              | 5.4.3 Direct or Absolute Addressing Mode           | 92  |

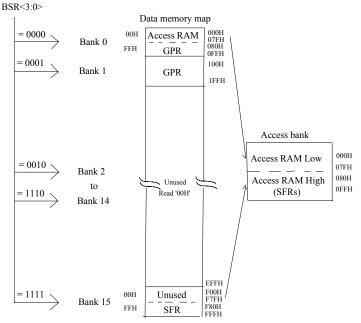

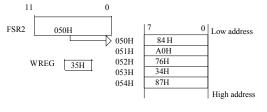

|              |              | 5.4.4 Indirect Addressing Mode                     | 93  |

|              |              | 5.4.5 Relative Addressing Mode                     | 97  |

|              |              | 5.4.6 Bit Addressing Mode                          | 99  |

|              | Quest        | ons and Problems 1                                 | 100 |

| <b>6.</b> A  | SSEM         | BLY LANGUAGE PROGRAMMING WITH THE PIC18F: PART 1 1 | 103 |

|              | 6.1          | Basic Concepts 1                                   | 103 |

|              | 6.2          | PIC18F Instruction Format 1                        | 108 |

|              | 6.3          | PIC18F Instruction Set                             | 110 |

|              |              | 6.3.1 Data Movement Instructions                   | 112 |

|              |              |                                                    | 118 |

|              |              | 8                                                  | 128 |

|              |              |                                                    | 131 |

|              |              | 1                                                  | 138 |

|              | QUES         | TIONS AND PROBLEMS                                 | 142 |

| <b>7.</b> A  | SSEM         | BLY LANGUAGE PROGRAMMING WITH THE PIC18F: PART 2 1 | 145 |

|              | 7.1          | PIC18F Jump/Branch Instructions 1                  | 145 |

|              | 7.2          |                                                    | 147 |

|              | 7.3          |                                                    | 152 |

|              | 7.4          |                                                    | 156 |

|              | 7.5          |                                                    | 159 |

|              | 7.6          |                                                    | 159 |

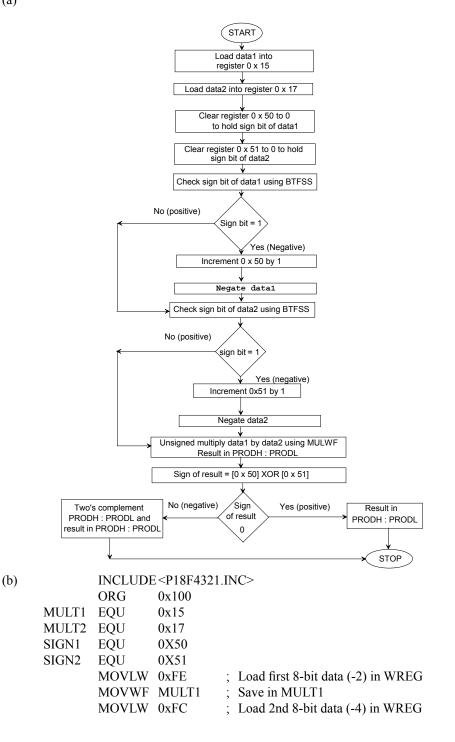

|              | 7.7          | 1 0                                                | 167 |

|              |              |                                                    | 167 |

|              |              | 6 6                                                | 170 |

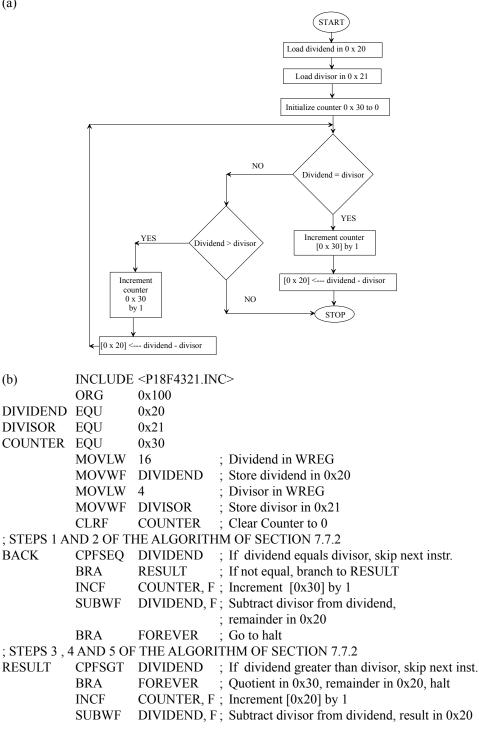

|              |              | 7.7.3 Signed Division Algorithm                    | 173 |

| Content  | 5         |                                                                                           | ix         |

|----------|-----------|-------------------------------------------------------------------------------------------|------------|

| 7.8      | Advar     | nced Programming Examples                                                                 | 174        |

| 7.9      |           | 3F Delay Routine                                                                          | 179        |

| Ques     | stions a  | nd Problems                                                                               | 182        |

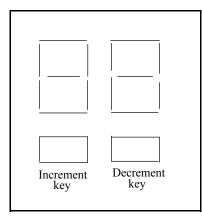

| 8. PIC18 | F HAR     | DWARE AND INTERFACING: PART 1                                                             | 187        |

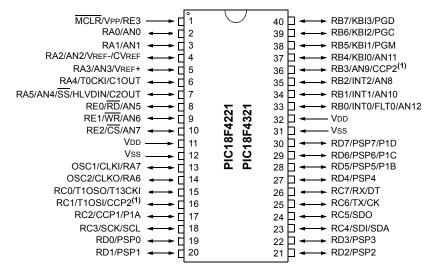

| 8.1      | PIC18     | BF Pins and Signals                                                                       | 187        |

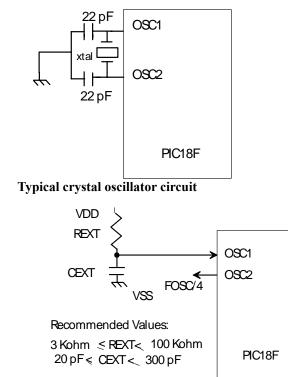

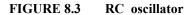

|          | 8.1.1     | Clock                                                                                     | 191        |

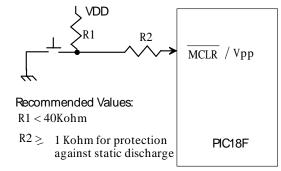

|          |           | PIC18F Reset                                                                              | 192        |

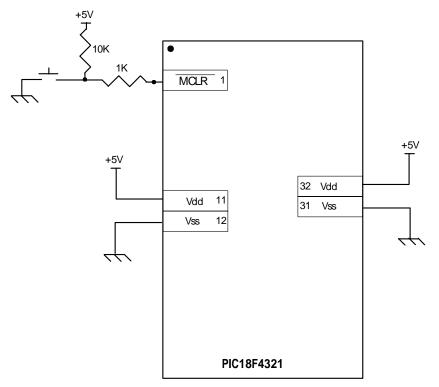

|          |           | A Simplified Setup for the PIC18F4321                                                     | 194        |

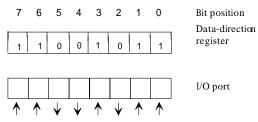

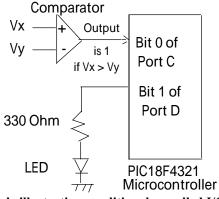

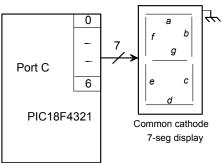

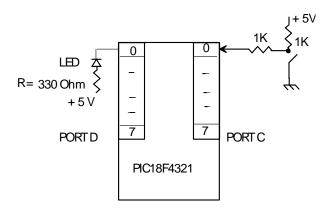

| 8.2      |           | 3F4321 I/O Ports                                                                          | 194        |

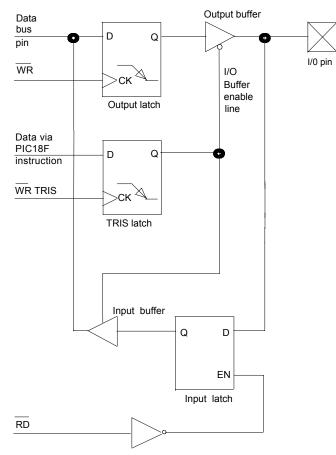

|          |           | PIC18F I/O Instructions                                                                   | 196        |

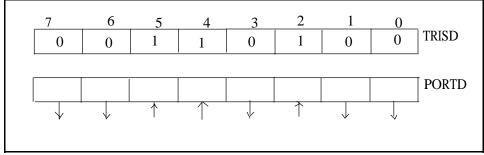

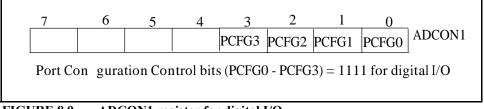

|          |           | Configuring PIC18F4321 I/O Ports                                                          | 197        |

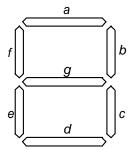

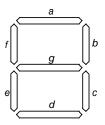

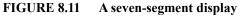

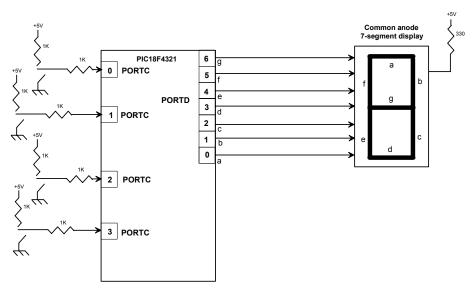

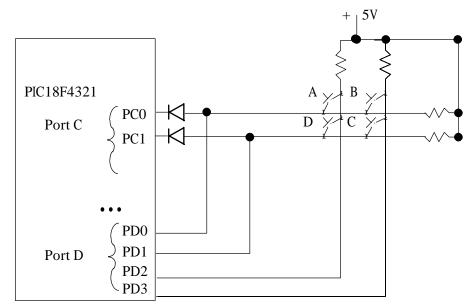

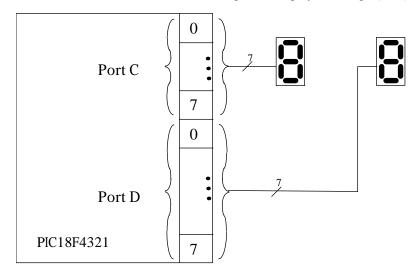

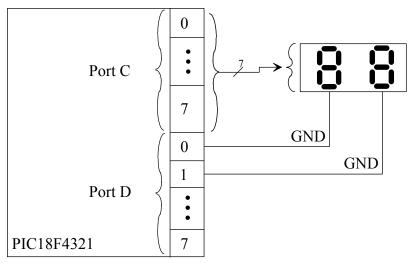

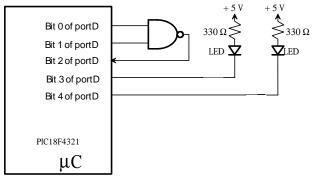

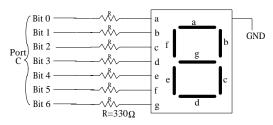

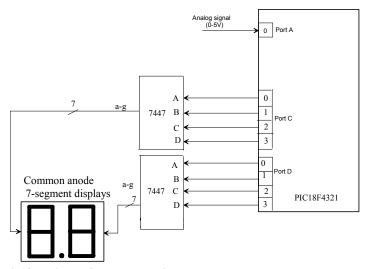

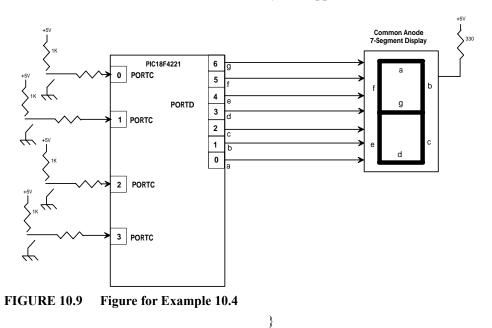

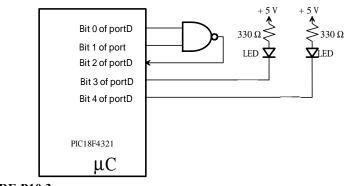

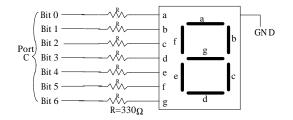

|          | 8.2.3     | Interfacing LEDs (Light Emitting Diodes) and Seven-segment                                | 4.0.0      |

| 0.0      | DIGIO     | Displays                                                                                  | 199        |

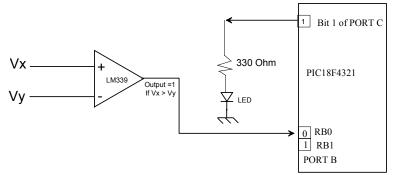

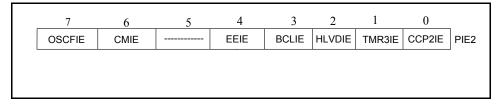

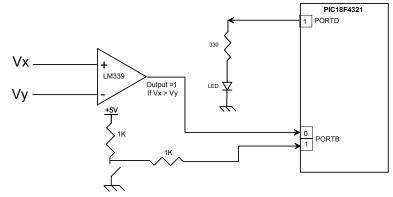

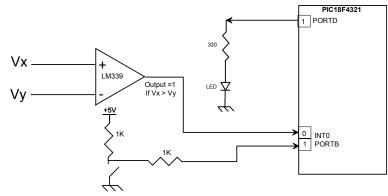

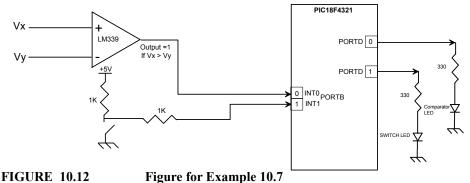

| 8.3      |           | BF Interrupts                                                                             | 204        |

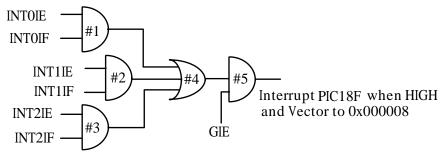

|          |           | Interrupt Procedure                                                                       | 205        |

|          |           | PIC18F Interrupt Types                                                                    | 206        |

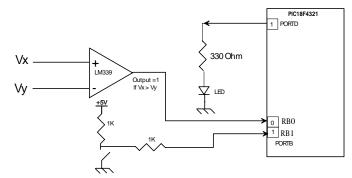

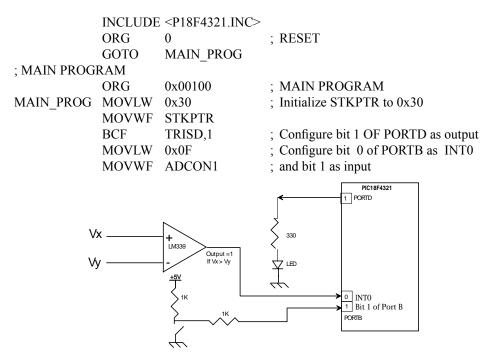

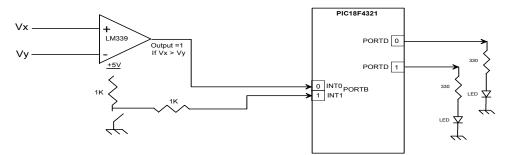

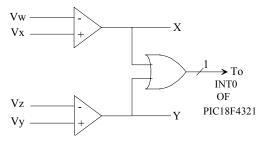

|          |           | PIC18F External Interrupts in Default Mode                                                | 206        |

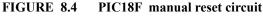

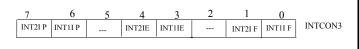

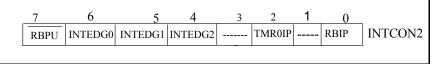

|          |           | Interrupt Registers and Priorities                                                        | 211<br>213 |

|          |           | Setting the Triggering Levels of INTn Pin Interrupts<br>Return from Interrupt Instruction | 213        |

|          |           | PORTB Interrupt-on-Change                                                                 | 213        |

|          |           | Context Saving During Interrupts                                                          | 214        |

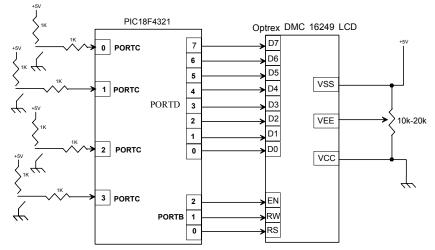

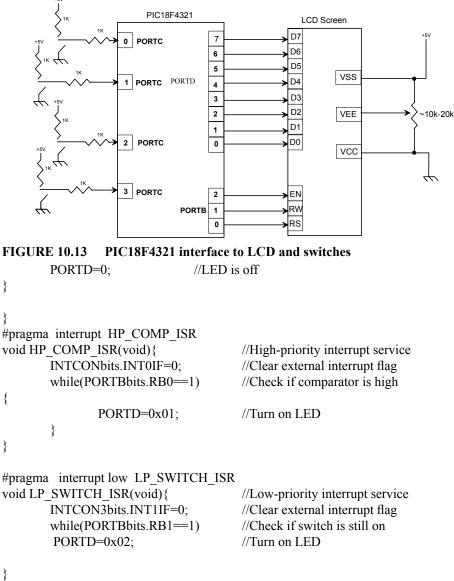

| 8.4      |           | 3F Interface to an LCD (Liquid Crystal Display)                                           | 217        |

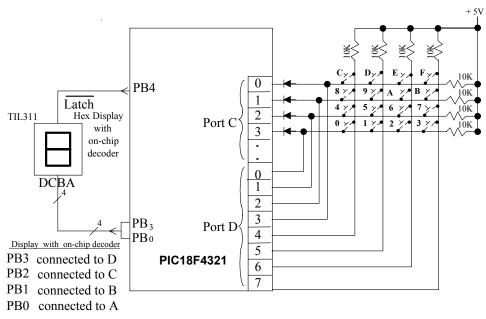

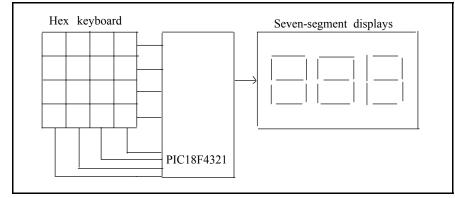

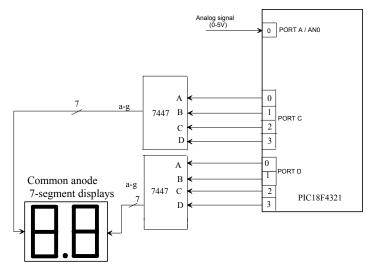

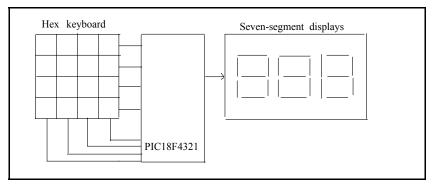

| 8.5      |           | acing PIC18F4321 to a Hexadecimal Keyboard and a Seven-segme                              |            |

| 0.0      | Displa    |                                                                                           | 219        |

|          |           | Basics of Keyboard and Display Interface to a Microcontroller                             | 221        |

|          |           | PIC18F4321 Interface to a Hexadecimal Keyboard and a                                      |            |

|          |           | Seven-segment Display                                                                     | 223        |

| Ques     | stions a  | nd Problems                                                                               | 230        |

| 9. PIC18 | FHAR      | DWARE AND INTERFACING: PART 2                                                             | 235        |

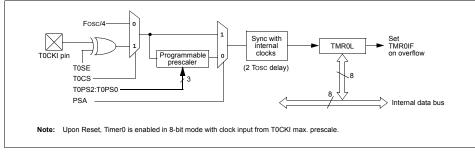

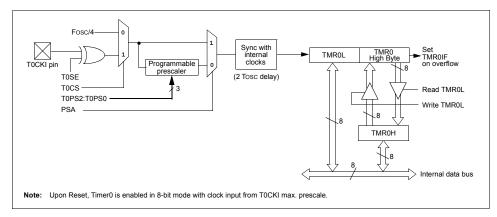

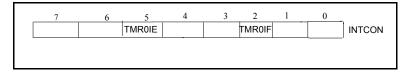

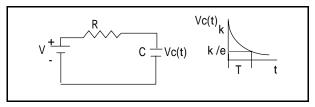

| 9.1      |           | BF Timers                                                                                 | 235        |

|          |           | Timer0                                                                                    | 236        |

|          | 9.1.2     | Timer1                                                                                    | 240        |

|          | 9.1.3     | Timer2                                                                                    | 244        |

|          | 9.1.4     | Timer3                                                                                    | 247        |

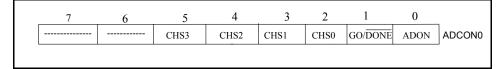

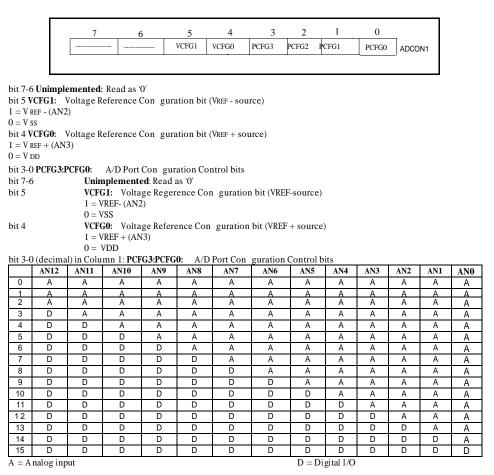

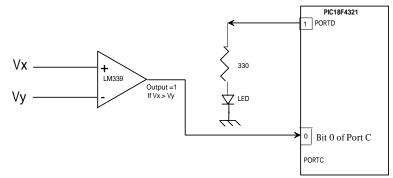

| 9.2      |           | Interface                                                                                 | 247        |

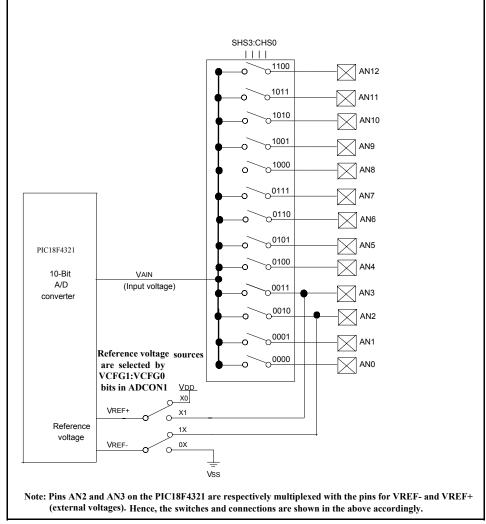

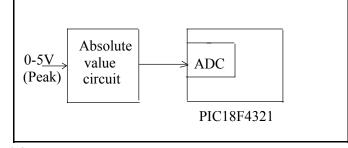

|          | 9.2.1     | On-chip A/D Converter                                                                     | 250        |

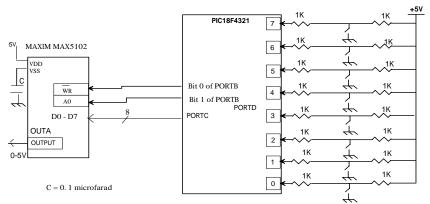

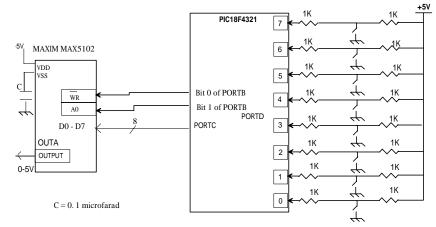

|          | 9.2.2     | Interfacing an External D/A (Digital-to-Analog) Converter to the                          |            |

|          |           | PIC18F4321                                                                                | 257        |

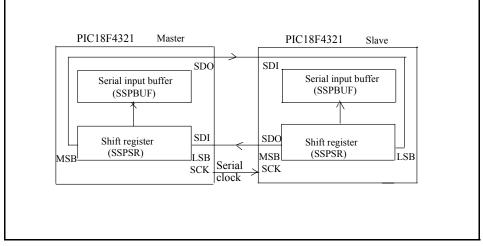

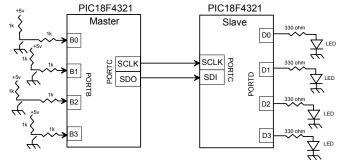

| 9.3      | Serial In |                                                                                           | 259        |

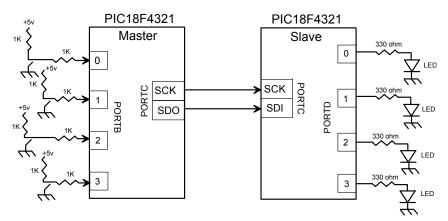

|          |           | Synchronous Serial Data Transmission                                                      | 259        |

|          |           | Asynchronous Serial Data Transmission                                                     | 260        |

|          |           | PIC18F Serial I/O                                                                         | 260        |

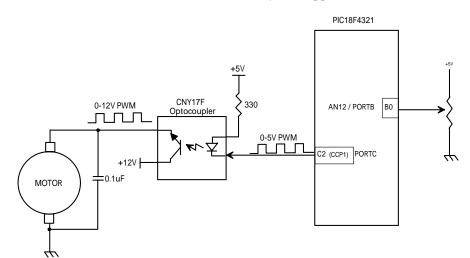

| 9.4      |           | 3F4321 Capture/Compare/PWM (CCP) Modules                                                  | 267        |

|          |           | CCP Registers                                                                             | 268        |

|          |           | CCP Modules and Associated Timers                                                         | 268        |

|          | 9.4.3     | PIC18F4321 Capture Mode                                                                   | 269        |

| 9.4.4 PIC18F4321 Compare Mode                                                                                            | 271        |

|--------------------------------------------------------------------------------------------------------------------------|------------|

| 9.4.5 PIC18F4321 PWM (Pulse Width Modulation) Mode                                                                       | 272        |

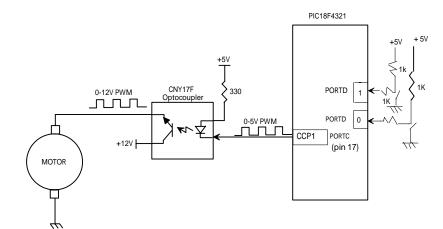

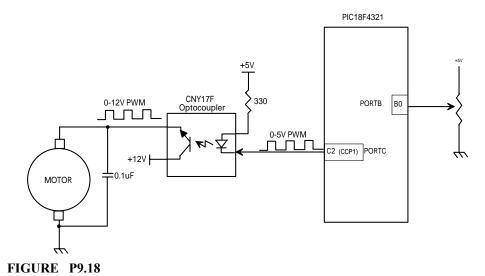

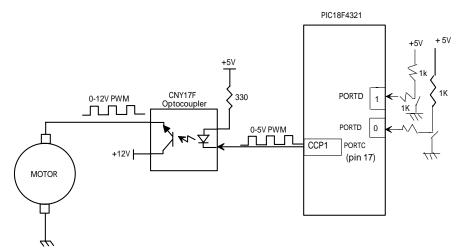

| 9.5 DC Motor Control                                                                                                     | 274        |

| Questions and Problems                                                                                                   | 277        |

| 10. BASICS OF PROGRAMMING THE PIC18F USING C                                                                             | 283        |

| 10.1 Introduction to C Language                                                                                          | 283        |

| 10.2 Data Types                                                                                                          | 287        |

| 10.3 Bit Manipulation Operators                                                                                          | 287        |

| 10.4 Control Structures                                                                                                  | 289        |

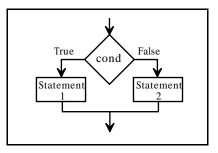

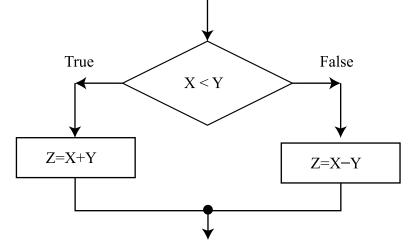

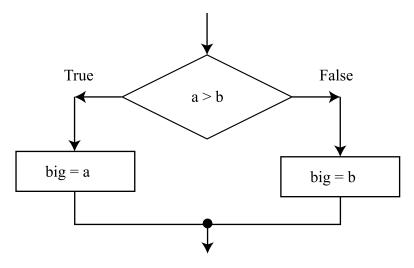

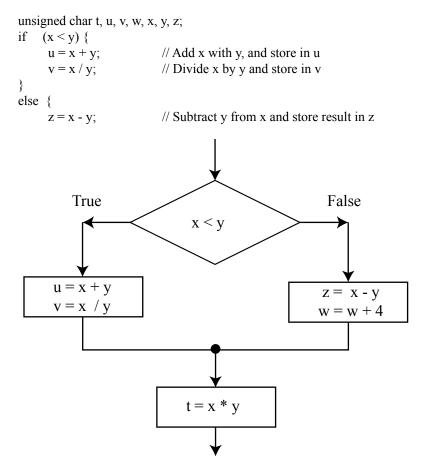

| 10.4.1 The if-else Construct                                                                                             | 289        |

| 10.4.2 The switch Construct                                                                                              | 292        |

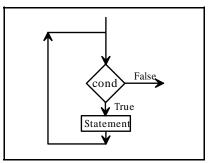

| 10.4.3 The while Construct                                                                                               | 293        |

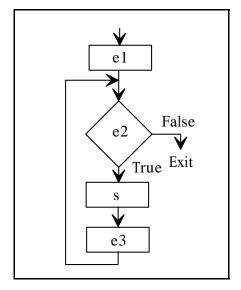

| 10.4.4 The for Construct                                                                                                 | 294        |

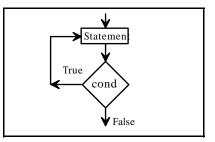

| 10.4.5 The do-while Construct                                                                                            | 296        |

| 10.5 Structures and Unions                                                                                               | 296        |

| 10.6 Functions in C                                                                                                      | 298        |

| 10.7 Macros                                                                                                              | 299        |

| <ul><li>10.8 Configuring PIC18F4321 I/O Ports Using C</li><li>10.9 Programming PIC18F4321 Interrupts Using C</li></ul>   | 299<br>304 |

| 10.9 Programming FICTOF4321 Interrupts Osing C<br>10.9.1 Specifying Interrupt Address Vector using the C18 Compiler      | 304        |

| 10.9.2 Assigning Interrupt Priorities Using the C18 Compiler                                                             | 305        |

| 10.9.2 Assigning interrupt Provinces Using the CPB Compiler<br>10.9.3 A Typical Structure for Interrupt Programs Using C | 305        |

| 10.10 Programming the PIC18F4321 Interface to LCD Using C                                                                | 310        |

| 10.11 PIC18F on-chip Timers                                                                                              | 314        |

| 10.12 Programming the PIC18F4321 on-chip A/D Converter Using C                                                           | 316        |

| 10.13 Interfacing an External D/A (Digital-to-Analog) Converter Using C                                                  | 319        |

| 10.14 PIC18F SPI Mode for Serial I/O Using C                                                                             | 320        |

| 10.15 Programming the PIC18F4321 CCP Modules Using C                                                                     | 322        |

| 10.16 DC Motor Control Using PWM Mode and C                                                                              | 325        |

| Questions and Problems                                                                                                   | 328        |

| APPENDIX A: ANSWERS TO SELECTED PROBLEMS                                                                                 | 337        |

| APPENDIX B: GLOSSARY                                                                                                     | 345        |

| APPENDIX C: PIC18F INSTRUCTION SET (ALPHABETICAL ORDER)                                                                  | 357        |

| APPENDIX D: PIC18F INTRUCTION SET — DETAILS                                                                              | 363        |

| APPENDIX E: PIC18F4321 SPECIAL FUNCTION REGISTERS                                                                        | 405        |

| APPENDIX F: TUTORIAL FOR ASSEMBLING AND DEBUGGING                                                                        |            |

| A PIC18F ASSEMBLY LANGUAGE PROGRAM USING THE                                                                             |            |

| MPLAB                                                                                                                    | 407        |

| APPENDIX G: TUTORIAL FOR COMPILING AND DEBUGGING A                                                                       |            |

| C-PROGRAM USING THE MPLAB                                                                                                | 437        |

| APPENDIX H: INTERFACING THE PIC18F4321 TO PERSONAL                                                                       |            |

| COMPUTER USING PICKIT™ 3                                                                                                 | 465        |

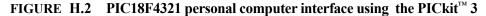

| H.1 INITIAL HARDWARE SETUP FOR THE PIC18F4321                                                                            | 465        |

#### Contents

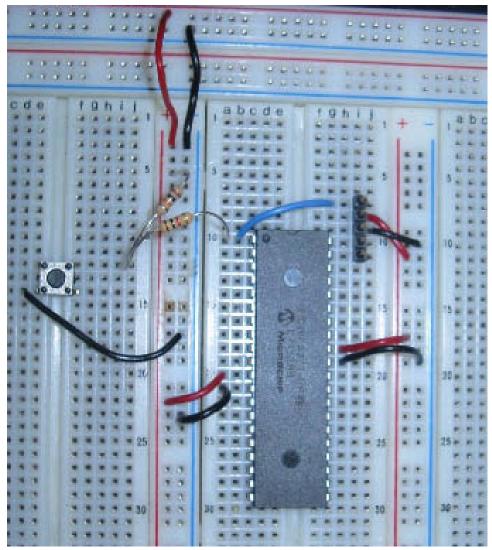

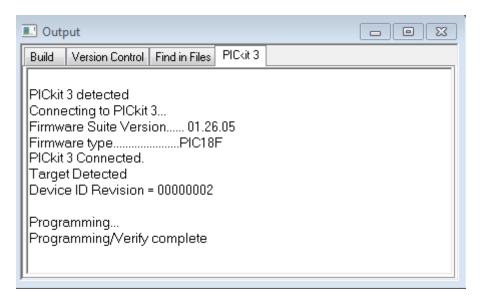

| Н.2     | CONNECTING THE PERSONAL COMPUTER (PC) TO THE PIC18F4321 VIA PICkit3 | 466 |

|---------|---------------------------------------------------------------------|-----|

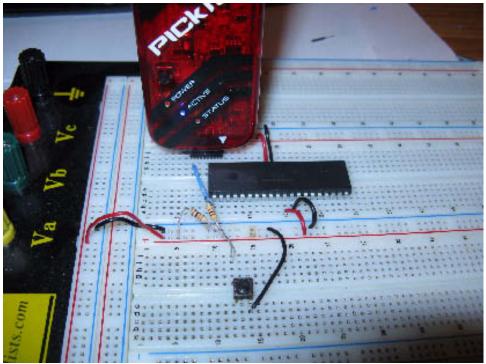

| H.3     | PROGRAMMING THE PIC18F4321 FROM PERSONAL COMPUTER USING THE PICkit3 | 468 |

| BIBLIOG |                                                                     | 471 |

| INDEX   |                                                                     | 473 |

xi

## PREFACE

Microcontrollers play an important role in the design of digital systems. They are found in a wide range of applications including office automation systems (copiers and fax machines), consumer electronics (microwave ovens), digital instruments, and robotics.

This book is written in a very simplified manner to present the fundamental concepts of assembly and C language programming and interfacing techniques associated with typical microcontrollers. Microchip Technology's PIC18F4321 is used for this purpose. The PIC18F family continues to be popular. The PIC18F family is an excellent educational tool for acquiring an understanding of both hardware and software aspects of typical microcontrollers.

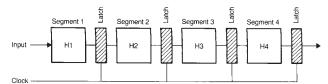

The PIC18F uses Harvard architecture with a RISC-based CPU. Conventional CPUs complete fetch, decode, and execute cycles of an instruction in sequence. However, the PIC18F uses pipelining, in which instruction fetch and execute cycles are overlapped. This speeds up the instruction execution time of the PIC18F. A brief coverage of CPU architectures, RISC vs. CISC, pipelining, assembly/C language programming, and I/O techniques associated with typical microcontrollers is provided in the first part of the book. These topics are then related to a popular member of the PIC18F family such as the PIC18F4321 in the second part of the book.

As far as the programming is concerned, assembly language programming is mostly covered in this book using the PIC18F. An adequate coverage of C is also provided. Although writing programs using C is easier than using assembly language, assembly language programming will provide an exposure to the internal architecture of microcontrollers. Furthermore, programming in assembly language may sometimes be useful for real-time systems.

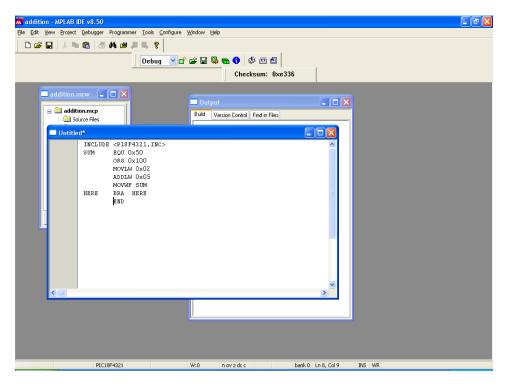

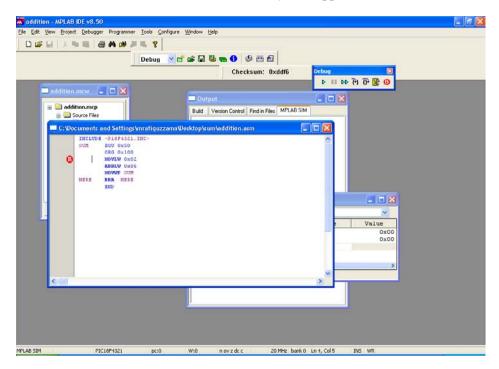

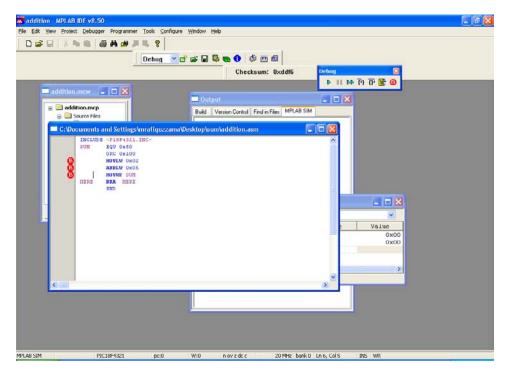

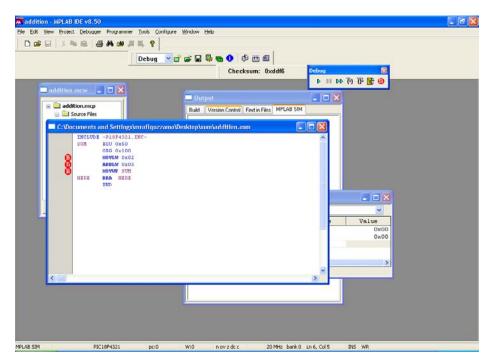

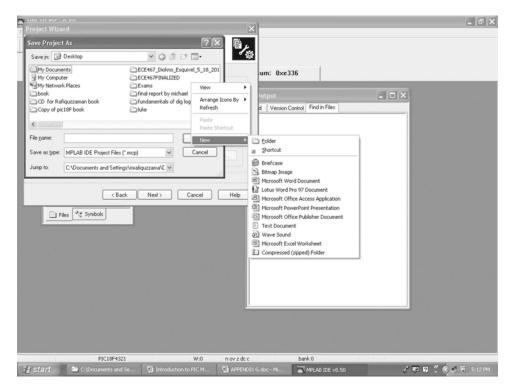

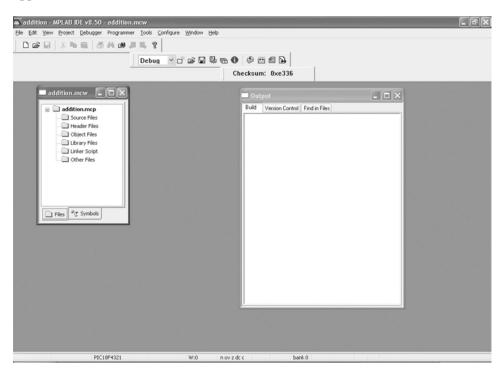

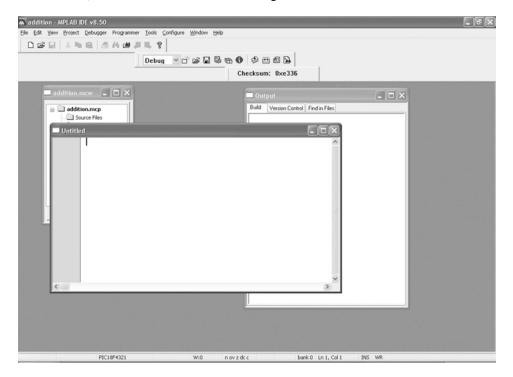

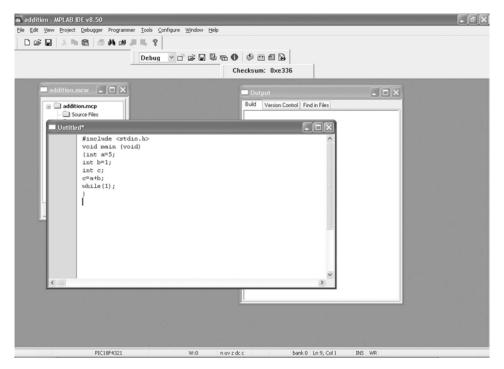

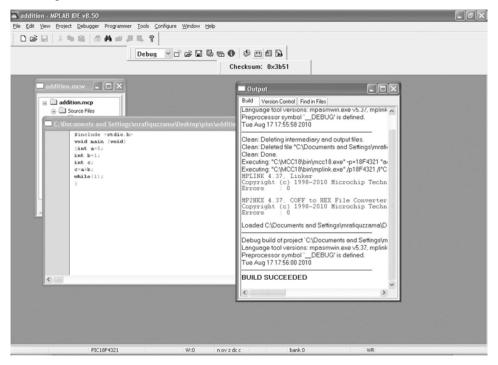

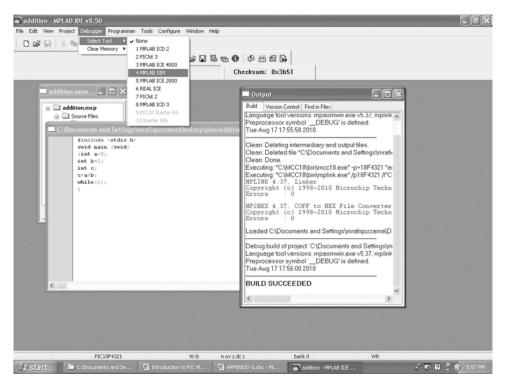

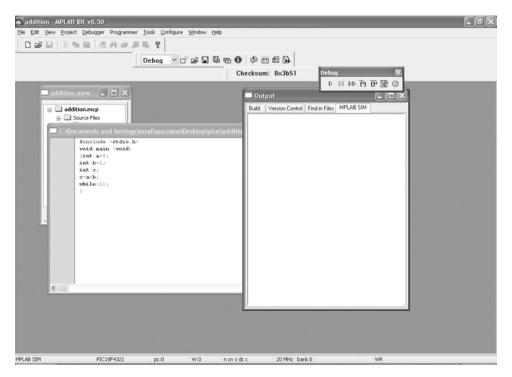

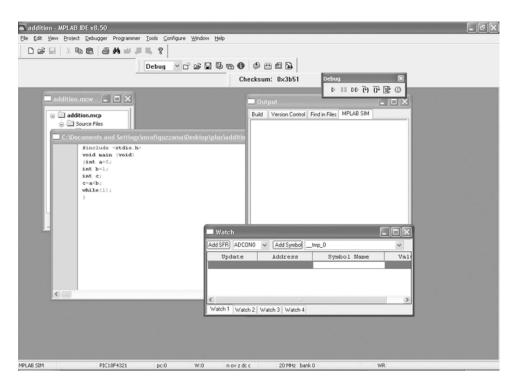

Several assembly and some C language programs along with I/O examples are developed using Microchip's MPLAB and PICkit<sup>TM</sup>3. The MPLAB software package includes a text editor, PIC18F assembler, C compiler, and a simulator. The PICkit<sup>TM</sup>3 is a programmer provided by Microchip. One can build an inexpensive PIC18F-based system on a breadboard using one of the PIC18F devices such as the PIC18F4321. The programmer can download the compiled or assembled programs using the PICkit<sup>TM</sup>3 from the personal computer or laptop, and then perform meaningful experiments. This is the most inexpensive way of implementing laboratory experiments using a typical microcontroller such as the PIC18F4321. Note that Appendix F provides a tutorial showing step-by-step procedure for assembling and debugging a PIC18F assembly language program using Microchip MPLAB PIC18F assembler/debugger. Appendix G, on the other hand, includes a tutorial showing step-by-step procedure for compiling and debbuging a C program using the MPLAB C18 compiler/debugger.

The book is self-contained and includes a number of basic topics. A background in basic digital logic and C language programming is assumed. Characteristics and principles common to typical microcontrollers are emphasized and basic microcontroller interfacing techniques are demonstrated via examples using the simplest possible devices, such as switches, LEDs, A/D and D/A converters, the hexadecimal keyboard, and seven-segment

and LCD displays. Most of the examples are implemented successfully in the laboratory.

The text is divided into 10 chapters. In Chapter 1, we provide a review of terminology, number systems, and evolution of microcontrollers. A comparison of the basic features of some members of the PIC18F family and typical microcontroller applications are also included.

Chapters 2 through 5 provide basic concepts needed to understand the material presented in Chapters 6 though 10. Chapter 2 covers typical microcontroller architectures. The concepts of CPU architecture, program and data memory units, pipelining, and RISC vs. CISC are included.

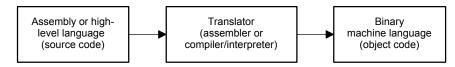

Chapter 3 contains programming concepts associated with typical microcontrollers. Topics include machine, assembly, and C language programming, typical addressing modes, and instruction sets.

Chapter 4 is focused on the memory organization and I/O (Input / Output) techniques associated with typical microcontrollers. The basic concepts associated with main memory array design, including memory maps, are also covered. Typical microcontroller input/output techniques including programmed I/O and interrupt I/O are included.

Chapter 5 includes PIC18F architecture and addressing modes. The PIC18F pipelining, register architecture, memory maps, and addressing modes are provided.

Chapters 6 through 9 form the nucleus of the book. The concepts of assembly language programming covered in Chapter 3 are demonstrated in Chapters 6 and 7 by means of a typical 8-bit microcontroller. A specific device from the PIC18F family such as the PIC18F4321 is used to illustrate the concepts. Several PIC18F assembly language programming examples are included.

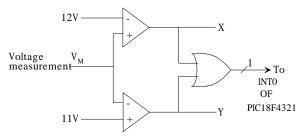

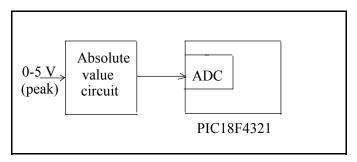

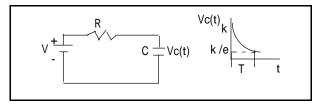

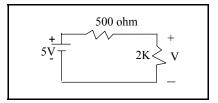

The I/O techniques covered in Chapter 4 are demonstrated in Chapters 8 and 9 using the PIC18F4321. Several I/O examples using PIC18F assembly language are also included. These chapters also demonstrate how the software and hardware work together by interfacing simple I/O devices such as switches, LEDs, and seven-segment displays to more advanced devices such as LCDs (Liquid Crystal Displays), hexadecimal keyboard, and A/D and D/A converters. The PIC18F timers and CCP (Compare/Capture/PWM) module along with Serial I/O are also covered. Typical examples include designing a PIC18F4321-based voltmeter using both programmed and interrupt I/O.

The concepts of C language programming covered in Chapter 3 are demonstrated in Chapter 10 using the PIC18F4321 microcontroller from an introductory point-of-view. Chapter 10 starts with a brief coverage of basics of C language, and then implements most of the assembly language programming examples in Chapters 8 and 9 using C. Typical C programs include I/O examples with LEDs and switches, PIC18F-based voltmeter, A/D and D/A converters, LCD displays, timers, and motor control using PWM (Pulse Width Modulation).

The book can easily be adopted as a text for a one- semester or one-quarter course in microcontrollers taught at the undergraduate level in electrical/computer engineering and computer science departments. The students are expected to have a background in C language and digital logic (both combinational and sequential) design. The book will also be useful for practicing microcontroller system designers. Practitioners of microcontroller-based applications will find more simplified explanations, together with examples and comparison considerations, than are found in manufacturers' manuals.

As mentioned before, emphasis is given in this book on assembly language programming using a typical microcontroller such as the PIC18F4321. Adequate coverage

#### Preface

of I/O and interfacing using C is included.

Since C language programming is prerequisite for this course on microcontrollers, coverage of I/O and interfacing using C would suffice. A basic coverage of assembly language programming using a typical microcontroller such as the PIC18F is provided.

The author is especially indebted to his colleague, Dr. R. Chandra, of California State Poly University, Pomona; to his student, Luke Stankiewicz; and to others for their valuable comments and for making constructive suggestions. The author also wishes to express his sincere appreciation to his student, Michael Nguyen for drawing several figures in the book, and to CJ Media of California for preparing the final version of the manuscript. The author is also grateful to his student, Sevada Isayan, and to Marc McComb and Rob Stransky of Microchip Technology, Inc. for their inspiration and support throughout the writing effort. Finally, the author is indebted especially to his deceased parents, who were primarily responsible for his accomplishments.

Pomona, California

M. RAFIQUZZAMAN

## CREDITS

The material cited here is used by permission of the sources listed below.

*Copyright of Microchip Technology, Inc. 2009, Used by Permission:* PIC18F4321 Family Data Sheet, DS39689F. All mnemonics of Microchip PIC18F Microcontroller Family are courtesy of Microchip Technology, Inc.

# 1 INTRODUCTION TO MICROCONTROLLERS

Digital systems are designed to store, process, and communicate information in digital form. They are found in a wide range of applications, including process control, communication systems, digital instruments, and consumer products. A digital computer, more commonly called simply a *computer*, is an example of a typical digital system.

A computer manipulates information in digital or, more precisely, binary form. A *binary number* has only two discrete values: zero or one. Each discrete value is represented by the OFF and ON status of an electronic switch called a *transistor*. All computers understand only binary numbers. Any decimal number (base 10, with ten digits from 0 to 9) can be represented by a binary number (base 2, with digits 0 and 1).

The basic blocks of a computer are the central processing unit (CPU), the memory, and the input/output (I/O). The CPU of a computer is basically the same as the brain of a human being; so computer memory is conceptually similar to human memory. A question asked of a human being is analogous to entering a program into a computer using an input device such as a keyboard, and a person answering a question is similar in concept to outputting the program result to a computer output device such as a printer. The main difference is that human beings can think independently, whereas computers can answer only questions for which they are programmed. Computer *hardware* includes such components as memory, CPU, transistors, nuts, bolts, and so on. Programs can perform a specific task, such as addition, if the computer has an electronic circuit capable of adding two numbers. Programmers cannot change these electronic circuits but can perform tasks on them using instructions.

Computer *software* consists of a collection of programs that contain instructions and data for performing a specific task. All programs, written using any programming language (e.g., C), must be translated into binary prior to execution by a computer because the computer understands only binary numbers. Therefore, a translator is necessary to convert such a program into binary, and this is achieved using a translator program called a *compiler*. Programs in the binary form of 1's and 0's are then stored in the computer memory for execution. Also, as computers can only add and compare, all operations, including subtraction, multiplication, and division, are performed by addition.

Due to advances in semiconductor technology, it is possible to fabricate a CPU on a single chip. The result is a *microprocessor*. Both metal-oxide semiconductor (MOS) and bipolar technologies are used in the fabrication process. The CPU can be placed on a single chip when MOS technology is used. However, several chips are required with bipolar technology. At present, HCMOS (high-speed complementary MOS) or BICMOS (combination of bipolar and HCMOS) technology is normally used to fabricate a microprocessor on a single chip. Along with the microprocessor chip, appropriate memory and I/O chips can be used to design a *microcomputer*. The pins on each one of these chips

can be connected to the proper lines on a system bus, which consists of address, data, and control lines. In the past, some manufacturers designed a complete microcomputer (CPU, memory, and I/O) on a single chip with limited capabilities. Single-chip microcomputers such as the Intel 8048 were used in a wide range of industrial and home applications.

*Microcontrollers* evolved from single-chip microcomputers. Microcontrollers are normally used for dedicated applications such as automotive systems, home appliances, and home entertainment systems. Typical microcontrollers include a CPU, memory, I/O, along with peripheral functions such as timers, A/D (analog-to-digital), and serial I/O all on a single chip. Microchip Technology's PIC (peripheral interface controller) is an example of a typical microcontroller.

In this chapter we first define some basic terms associated with microcontrollers. We then describe briefly the evolution of microcontrollers. Finally, typical microcontroller-based applications are included.

#### 1.1 Explanation of Terms

Before we go on, it is necessary to understand some basic terms.

- *Address* is a pattern of 0's and 1's that represents a specific location in memory or a particular I/O device. An 8-bit microcontroller with 16 address bits can produce 2<sup>16</sup> unique 16-bit patterns from 000000000000000 to 1111111111111111, representing 65,536 different address combinations (addresses 0 to 65,535).

- *Addressing mode* is the manner in which the microcontroller determines the operand (data) and destination addresses during execution of an instruction.

- *Arithmetic-logic unit* (ALU) is a digital circuit that performs arithmetic and logic operations on two *n*-bit digital words. The value of *n* for microcontrollers can be 8-bit or 16-bit. Typical operations performed by an ALU are addition, subtraction, ANDing, ORing, and comparison of two *n*-bit digital words. The size of the ALU defines the size of the microcontroller. For example, an 8-bit microcontroller contains an 8-bit ALU.

- *Big endian* convention is used to store a 16-bit number such as 16-bit data in two bytes of memory locations as follows: the low memory address stores the high byte while the high memory address stores the low byte. The Motorola/Freescale HC11 8-bit microcontroller follows the big endian format.

- *Bit* is an abbreviation for the term *binary digit*. A binary digit can have only two values, which are represented by the symbols 0 and 1, whereas a decimal digit can have 10 values, represented by the symbols 0 through 9. The bit values are easily implemented in electronic and magnetic media by two-state devices whose states portray either of the binary digits 0 and 1. Examples of such two-state devices are a transistor that is conducting or not conducting, a capacitor that is charged or discharged, and a magnetic material that is magnetized north to south or south to north.

- *Bit size* refers to the number of bits that can be processed simultaneously by the basic arithmetic circuits of a microcontroller. A number of bits taken as a group in this manner is called a *word*. For example, an 8-bit microcontroller can process an 8-bit word. An 8-bit word is referred to as a *byte*, and a 4-bit word is known as a *nibble*.

#### Introduction to Microcontrollers

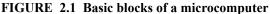

- Bus consists of a number of conductors (wires) organized to provide a means of communication among different elements in a microcontroller system. The conductors in a bus can be grouped in terms of their functions. A microcontroller normally has an address bus, a data bus, and a control bus. Address bits are sent to memory or to an external device on the *address bus*. Instructions from memory, and data to/from memory or external devices, normally travel on the *data bus*. Control signals for the other buses and among system elements are transmitted on the *control bus*. Buses are sometimes *bidirectional*; that is, information can be transmitted in either direction on the bus, but normally in only one direction at a time.

- *Clock* is analogous to human heart beats. The microcontroller requires synchronization among its components, and this is provided by a *clock* or timing circuits.

- *CPU* (Central Processing Unit) contains several registers (memory elements), an ALU, and a control unit. Note that the control unit translates instructions and performs the desired task. The number of peripheral devices depends on the particular application involved and may even vary within an application.

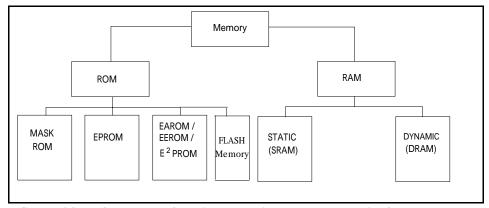

- *EEPROM* or *E*<sup>2</sup>*PROM* (Electrically Erasable Programmable ROM) is nonvolatile. EEPROMs can be programmed without removing the chip from the socket. EEPROMs are called Read Most Memories (RMMs), because they have much slower write times than read times. Therefore, these memories are usually suited for applications when mostly reading rather than writing is performed. An example of EEPROM is the 2864 (8K x 8).

- *EPROM* (Erasable Programmable ROM) is nonvolatile. EPROMs can be programmed and erased. The EPROM chip must be removed from the socket for programming. This memory is erased by exposing the chip to ultraviolet light via a lid or window on the chip. Typical erase times vary between 10 and 30 minutes. The EPROM is programmed by inserting the chip into a socket of the EPROM programmer, and providing proper addresses and voltage pulses at the appropriate pins of the chip. An example of EPROM is the 2764 (8K x 8).

- *Flash memory* is designed using a combination of EPROM and EEPROM technologies. Flash memory was invented by Toshiba in the mid 1980s and is nonvolatile. Flash memory can be programmed electrically while embedded on the board. One can change multiple bytes at a time. An example of flash memory is the Intel 28F020 (256K x 8). Flash memory is typically used in cell phones and digital cameras.

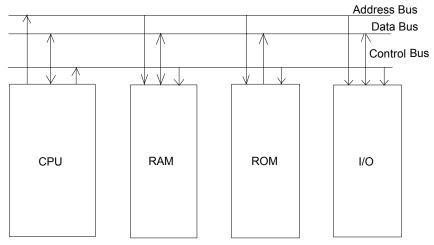

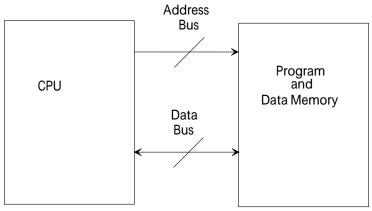

- *Harvard architecture* is a type of CPU architecture that uses separate instruction and data memory units along with separate buses for instructions and data. This means that these processors can execute instructions and access data simultaneously. Processors designed with this architecture require four buses for program memory and data memory. These are one data bus for instructions, one address bus for addresses of data. The sizes of the address and data buses for instructions may be different from the address and data buses for data. Several microcontrollers including the PIC18F are designed using the Harvard architecture. This is because it is inexpensive to implement these buses inside the chip since both program and data memories are internal to the chip.

- *Instruction set* of a microcontroller is a list of commands that the microcontroller is designed to execute. Typical instructions are ADD, SUBTRACT, and STORE. Individual instructions are coded as unique bit patterns that are recognized and executed by the microcontroller. If a microcontroller has three bits allocated to the representation of instructions, the microcontroller will recognize a maximum of 2<sup>3</sup>, or eight, different instructions. The microcontroller will then have a maximum of eight instructions in its instruction set. It is obvious that some instructions will be more suitable than others to a particular application. For example, in a control application, instructions inputting digitized signals to the processor and outputting digital control variables to external circuits are essential. The number of instructions necessary in an application will directly influence the amount of hardware in the chip set and the number and organization of the interconnecting bus lines.

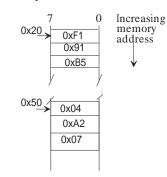

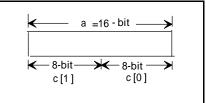

- *Little endian* convention is used to store a 16-bit number such as 16-bit data in two bytes of memory locations as follows: the low memory address stores the low byte while the high memory address stores the high byte. The PIC18F microcontroller follows the little endian format.

- *Microcomputer* typically consists of a microprocessor (CPU) chip, input and output chips, and memory chips in which programs (instructions and data) are stored.

- *Microcontroller* is implemented on a single chip containing a CPU, memory, and IOP (I/O and peripherals). Note that a typical IOP contains the I/O unit of a microcomputer, timers, an A/D (analog-to-digital) converter, analog comparators, serial I/O, and other peripheral functions (to be discussed later).

- *Microprocessor* is the CPU of a microcomputer contained on a single chip, and must be interfaced with peripheral support chips in order to function.

- *Pipelining* is a technique that overlaps instruction fetch (instruction read) with execution. This allows a microcontroller's processing operation to be broken down into several steps (dictated by the number of pipeline levels or stages) so that the individual step outputs can be handled by the microcontroller in parallel. Pipelining is often used to fetch the microcontroller's next instruction while executing the current instruction, which speeds up the overall operation of the micro controller considerably. Microchip technology's PIC18F (8-bit microcontroller) uses a two-stage instruction pipeline in order to speed up instruction.

- Program contains instructions and data. Two conventions are used to store a 16-bit number such as 16-bit data in two bytes of memory locations. These are called little endian and big endian byte ordering. In little endian convention, the low memory address stores the low byte while the high memory address stores the high byte. For example, the 16-bit hexadecimal number 2050 will be stored as two bytes in two 16-bit locations (Hex 5000 and Hex 5001) as follows: address 5000 will contain 50 and address 5001 will store 20. In big endian convention, on the other hand, the low memory address stores the high byte while the high memory address stores the low byte. For example, the same 16-bit hexadecimal number 2050 will be stored as two bytes in two 16-bit locations (Hex 5000 and Hex 5001) as follows: address 5000 will contain 50 and address 5001 will store 50. Motorola / Freescale HC11 (8-bit microcontroller) follows big endian convention. Microchip PIC18F (8-bit microcontroller), on the other hand, follows the little endian format.

#### Introduction to Microcontrollers

- *Random-access memory* (RAM) is a storage medium for groups of bits or words whose contents cannot only be read but can also be altered at specific addresses. A RAM normally provides *volatile storage*, which means that its contents are lost in case power is turned off. There are two types of RAM: static RAM (SRAM), and dynamic RAM (DRAM). *Static RAM* stores data in flip-flops. Therefore, this memory does not need to be refreshed. An example of SRAM is 6116 (2K x 8). *Dynamic RAM*, on the other hand, stores data in capacitors. That is, it can hold data for a few milliseconds. Hence, dynamic RAMs are refreshed typically by using external refresh circuitry. Dynamic RAMs (DRAMs) are used in applications requiring large memory. DRAMs have higher densities than SRAMs. Typical examples of DRAMs are the 4464 (64K x 4), 44256 (256K x 4), and 41000 (1M x 1). DRAMs are inexpensive, occupy less space, and dissipate less power than SRAMs.

- *Read-only memory* (ROM) is a storage medium for the groups of bits called *words*, and its contents cannot normally be altered once programmed. A typical ROM is fabricated on a chip and can store, for example, 2048 eight-bit words, which can be accessed individually by presenting to it one of 2048 addresses. This ROM is referred to as a 2K by 8-bit ROM. 10110111 is an example of an 8-bit word that might be stored in one location in this memory. A ROM is a *nonvolatile storage* device, which means that its contents are retained in case power is turned off. Because of this characteristic, ROMs are used to store permanent programs (instructions and data).

- *Reduced Instruction Set Computer* (RISC) contains a simple instruction set. In contrast, a *Complex Instruction Set Computer* (CISC) contains a large instruction set. The PIC18F is a RISC-based microcontroller whereas Motorola/Freescale HC11 is a CISC-based microcontroller.

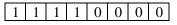

- *Register* can be considered as volatile storage for a number of bits. These bits may be entered into the register simultaneously (in parallel) or sequentially (serially) from right to left or from left to right, 1 bit at a time. An 8-bit register storing the bits 11110000 is represented as follows:

• von Neumann (Princeton) architecture uses a single memory unit and the same bus for accessing both instructions and data. Although CPUs designed using this architecture are slower compared to Harvard architecture, since instructions and data cannot be accessed simultaneously because of the single bus, typical microprocessors such as the Pentium use this architecture. This is because memory units such as ROMs, EPROMs, and RAMs are external to the microprocessor. This will require almost half the number of wires on the mother board because address and data pins for only two buses rather than four buses (Harvard architecture) are required. This is the reason Harvard architecture would be very expensive if utilized in designing microprocessors. Note that microcontrollers using Harvard architecture internally will have to use von Neumann architecture externally. Texas Instrument's MSP 430 uses the von Neumann architecture.

#### 1.2 Microcontroller Data Types

In this section we discuss data types used by typical microcontrollers: unsigned and signed binary numbers, ASCII (American Standard Code for Information Interchange), EBCDIC (extended binary coded decimal interchange code) and binary-coded decimal (BCD).

#### 1.2.1 Unsigned and Signed Binary Numbers

An *unsigned binary number* has no arithmetic sign and therefore is always positive. Typical examples are your age or a memory address, which are always positive numbers. An 8-bit unsigned binary integer represents all numbers from  $00_{16}$  through FF<sub>16</sub>( $0_{10}$  through 255<sub>10</sub>).

A signed binary number, on the other hand, includes both positive and negative numbers. It is represented in the microcontroller in two's complement form. For example, the decimal number +15 is represented in 8-bit two's complement form as 00001111 (binary) or 0F (hexadecimal). The decimal number -15 can be represented in 8-bit two's complement form as 11110001 (binary) or F1 (hexadecimal). Also, the most significant bit (MSB) of a signed number represents the sign of the number. For example, bit 7 of an 8-bit number, bit 15 of a 16-bit number, and bit 31 of a 32-bit number represent the signs of the respective numbers. A "0" at the MSB represents a positive number; a "1" at the MSB represents a negative number. Note that the 8-bit binary number 1111111 is  $255_{10}$  when represented as an unsigned number. On the other hand,  $1111111_2$  is  $-1_{10}$  when represented as a signed number.

One can convert an unsigned binary number from lower to higher length using zero extension. For example, an 8-bit unsigned number FF (hex) can be converted to a 16-bit unsigned number 00FF (hex) by extending 0's to the upper byte of 00FF (hex). Both FF (hex) and 00FF (hex) have the same decimal value of 255. This is called zero extension. Zero extension is useful for performing arithmetic operations between two unsigned binary numbers of different lengths.

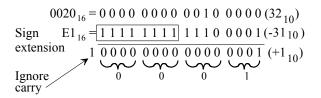

A signed binary number, on the other hand, can be converted from lower to higher length using sign extension. For example, an 8-bit signed number FF (hex) can be converted to a 16-bit signed number FFFF (hex) by extending the sign bit ('1' in this case) to the upper byte of FFFF (hex). Both FF (hex) and FFFF (hex) have the same decimal value of -1. Sign extension is useful for performing arithmetic operations between two signed binary numbers of different lengths.

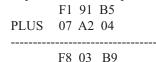

Sign extension is useful when one wants to perform an arithmetic operation on two signed numbers of different lengths. For example, the 16-bit signed number 0020 (hex) can be added with the 8-bit signed number E1 (hex) by sign-extending E1 as follows:

An error (indicated by overflow in a microcontroller) may occur while performing two's complement arithmetic. The microcontroller automatically sets an overflow bit to 1 if the result of an arithmetic operation is too big for the microcontroller's maximum word size; otherwise it is reset to 0. For signed arithmetic operations such as addition, the overflow  $V = C_f \oplus C_p$ , where  $C_f$  is the final carry and  $C_p$  is the previous carry. This can be illustrated by the following examples.

Consider the following examples for 8-bit numbers. Let  $C_f$  be the final carry (carry out of the most significant bit or sign bit) and  $C_p$  be the previous carry (carry out of bit 6 or seventh bit). We will show by means of numerical examples that as long as  $C_f$  and  $C_p$  are the same, the result is always correct. If, however,  $C_f$  and  $C_p$  are different, the result is incorrect and sets the overflow bit to 1. Now, consider the following cases.

*Case 1:*  $C_f$  and  $C_p$  are the same.

$$C_{f}=0 \begin{array}{c} 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 & 0 & 1 \\ 0 & 1 & 1 & 0 & 0 & 0 & 1 & 0 \\ C_{f}=1 & & & & & \\ C_{p}=1 & & & & & \\ C_{p}=1 & & & & & \\ \end{array}$$

Therefore, when  $C_f$  and  $C_p$  are either both 0 or both 1, a correct answer is obtained. *Case 2:*  $C_f$  and  $C_p$  are different.

$C_f = 0$  and  $C_p = 1$  give an incorrect answer because the result shows that the addition of two positive numbers is negative.

$$C_{f} = 1 \begin{array}{c} 1 & 0 & 1 & 1 & 0 & 1 & 1 & 0 \\ 1 & 0 & 0 & 0 & 0 & 0 & 1 \\ \hline 1 & 0 & 0 & 1 & 1 & 0 & 1 & 1 & 1 \\ 0 & 0 & 1 & 1 & 0 & 1 & 1 & 1 \\ C_{f} = 0 \end{array} \begin{array}{c} -4A_{16} \\ -7E_{16} \\ +37_{16} \end{array}$$

$C_f = 1$  and  $C_p = 0$  provide an incorrect answer because the result indicates that the addition of two negative numbers is positive. Hence, the overflow bit (V) will be set to zero if the carries  $C_f$  and  $C_p$  are the same, that is, if both  $C_f$  and  $C_p$  are either 0 or 1. On the other hand, the overflow bit (V) will be set to 1 if carries  $C_f$  and  $C_p$  are different. The relationship among  $C_f$ ,  $C_p$ , and V can be summarized in a truth table as follows:

|                                      | mp                   | uts                                | Output             |

|--------------------------------------|----------------------|------------------------------------|--------------------|

|                                      | $C_{\mathrm{f}}$     | C <sub>p</sub>                     | V                  |

|                                      | 0                    | 0                                  | 0                  |

|                                      | 0                    | 1                                  | 1                  |

|                                      | 1                    | 0                                  | 1                  |

|                                      | 1                    | 1                                  | 0                  |

| From the truth table, overflow $V =$ | $\overline{C_f} C_p$ | $+ C_{\rm f} \overline{C_{\rm p}}$ | $= C_f \oplus C_p$ |

Note that the symbol  $\oplus$  represents exclusive-OR logic operation. Exclusive-OR means that when two inputs are the same (both one or both zero), the output is zero. On the other hand, if two inputs are different, the output is one. The overflow can be considered as an output while  $C_f$  and  $C_p$  are the two inputs. The answer is incorrect when the overflow bit is set to 1; the answer is correct if the overflow bit is 0.

Typical 16- and 32-bit microprocessors such as Motorola/Freescale 68000/68020 have separate unsigned and signed multiplication and division instructions as follows: MULU (multiply two unsigned numbers), MULS (multiply two signed numbers), DIVU (divide two unsigned numbers), and DIVS (divide two signed numbers). It is important for the programmer to understand clearly how to use these instructions.

For example, suppose that it is desired to compute  $X^2/255$ . If X is a signed 8-bit number, the programmer should use the MULS instruction to compute X \* X which is always unsigned (the square of a number is always positive), and then use DIVU to compute  $X^2/255$  (16-bit by 8-bit unsigned divide) since  $255_{10}$  is positive. But if the programmer uses DIVS, both X \* X and  $255_{10}$ (FF<sub>16</sub>) will be interpreted as signed numbers. FF<sub>16</sub> will be interpreted as  $-1_{10}$ , and the result will be wrong. On the other hand, if X is an unsigned number, the programmer needs to use MULU and DIVU to compute  $X^2/255$ .

The PIC18F microcontroller includes unsigned multiplication instruction. However, the PIC18F does not provide any signed multiplication and signed or unsigned division instructions. However, as shown in chapter 7, these instructions can be achieved by writing subroutines using PIC18F instructions.

#### 1.2.2 ASCII and EBCDIC Codes

If it is to be very useful, a microcontroller must be capable of handling nonnumeric information. In other words, a microcontroller must be able to recognize codes that represent numbers, letters, and special characters. These codes are classified as alphanumeric or character codes. A complete and adequate set of necessary characters includes the following:

- 26 lowercase letters

- 26 uppercase letters

- 10 numerical digits (0-9)

- Approximately 25 special characters, which include +, /, #, %, and others.

This totals 87 characters. To represent 87 characters with some type of binary code would require at least 7 bits. With 7 bits, there are  $2^7 = 128$  possible binary numbers; 87 of these combinations of 0 and 1 bits serve as the code groups representing the 87 different characters.

Two alphanumerical codes are the American Standard Code for Information Interchange (ASCII) and the extended binary-coded-decimal interchange code (EBCDIC). ASCII is typically used with microcontrollers; IBM uses EBCDIC code. Eight bits are used to represent characters, although 7 bits suffice, because the eighth bit is frequently used to test for errors and is referred to as a *parity bit*. It can be set to 1 or 0 so that the number of 1 bits in the byte is always odd or even.

Note that decimal digits 0 through 9 are represented by  $30_{16}$  through  $39_{16}$  in ASCII. On the other hand, these decimal digits are represented by  $F0_{16}$  though  $F9_{16}$  in EBCDIC. Note that ASCII and unicode are widely used these days. EBCDIC is outdated. However, ASCII and EBCDIC are used in the following example merely for illustrative purposes.

A microcontroller program is usually written for code conversion when input/ output devices of different codes are connected to the microcontroller. For example, suppose that it is desired to enter the number 5 into a computer via an ASCII keyboard and to print this number on an EBCDIC printer. The ASCII keyboard will generate  $35_{16}$  when the number 5 is pushed. The ASCII code  $35_{16}$  for the decimal digit 5 enters the microcontroller and resides in the memory. To print the digit 5 on the EBCDIC printer, a program must be written that will convert the ASCII code  $35_{16}$  for 5 to its EBCDIC code,  $F5_{16}$ . The output of this program is  $F5_{16}$ . This will be input to the EBCDIC printer. Because the printer understands only EBCDIC codes, it inputs the EBCDIC code  $F5_{16}$  and prints the digit 5. Typical microprocessors such as the Intel Pentium include instructions to provide correct unpacked BCD after performing arithmetic operations in ASCII. The Pentium instruction AAA (ASCII adjust for addition) is such an instruction. The PIC18F does not provide such an instruction.

#### 1.2.3 Unpacked and Packed Binary-Coded-Decimal Numbers

The 10 decimal digits 0 through 9 can be represented by their corresponding 4-bit binary numbers. The digits coded in this fashion are called *binary-coded-decimal digits* in 8421 code, or BCD digits. Two unpacked BCD bytes are usually packed into a byte to form *packed BCD*. For example, two unpacked BCD bytes  $02_{16}$  and  $05_{16}$  can be combined as a packed BCD byte  $25_{16}$ .

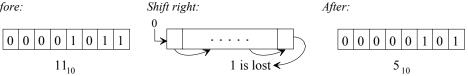

Let us consider entering data decimal 24 via an ASCII keyboard into a microcontroller. Two keys (2 and 4) will be pushed on the ASCII keyboard. This will generate 32 and 34 (32 and 34 are ASCII codes in hexadecimal for 2 and 4, respectively) inside the microcontroller. A program can be written to convert these ASCII codes into unpacked BCD  $02_{16}$  and  $04_{16}$ , and then to convert to packed BCD 24 or to binary inside the microcontroller to perform the desired operation. Unpacked BCD  $02_{16}$  and  $04_{16}$  can be converted into packed BCD 24 ( $00100100_2$ ) by logically shifting  $02_{16}$  four times to the left to obtain  $20_{16}$ , then logically ORing with  $04_{16}$ . On the other hand, to convert unpacked BCD  $02_{16}$  and  $04_{16}$  to obtain  $00011000_2$  (the binary equivalent of 24).

Note that BCD correction (adding 6) is necessary for the following:

i) if the binary sum is greater than or equal to decimal 16 (this will generate a carry of 1)ii) if the binary sum is 1010 through 1111

For example, consider adding packed BCD numbers 97 and 39:

| 97                      | 1001                    | 0111                    | BCD for 97           |

|-------------------------|-------------------------|-------------------------|----------------------|

| <u>+39</u>              | 0011                    | 1001                    | BCD for 39           |

| 136                     | 1101                    | 0000                    | invalid sum          |

|                         | +0110                   | +0110                   | add 6 for correction |

| $\underbrace{0001}_{1}$ | $\underbrace{0011}_{3}$ | $\underbrace{0110}_{6}$ | ← correct answer 136 |

111←Intermediate Carries

Typical 32-bit microprocessors such as the Motorola 68020 include PACK and UNPK instructions for converting an unpacked BCD number to its packed equivalent, and vice versa. The PIC18F microcontroller contains an instruction called DAW, which provides the correct BCD result after binary addition of two packed BCD numbers.

#### **1.3** Evolution of the Microcontroller

The Intel Corporation is generally acknowledged as the company that introduced the first microprocessor successfully into the marketplace. Its first microprocessor, the 4004, was introduced in 1971 and evolved from a development effort while a calculator chip set was being made. The 4004 microprocessor was the central component in the chip set, which was called the MCS-4. The other components in the set were a 4001 ROM, a 4002 RAM, and a 4003 shift register.

Shortly after the 4004 appeared in the commercial marketplace, three other general-purpose microprocessors were introduced: the Rockwell International 4-bit PPS-4, the Intel 8-bit 8008, and the National Semiconductor 16-bit IMP-16. Other companies, such as General Electric, RCA, and Viatron, also made contributions to the development of the microprocessor prior to 1971.

The microprocessors introduced between 1971 and 1972 were first-generation systems designed using PMOS technology. In 1973, second-generation microprocessors such as the Motorola 6800 and the Intel 8080 (8-bit microprocessors) were introduced. The second-generation microprocessors were designed using NMOS technology. This technology resulted in a significant increase in instruction execution speed over PMOS and higher chip densities. Since then, microprocessors such as the Intel 8085, the Zilog Z80, and the Motorola 6800/6809 were introduced based on second-generation microprocessors. A third-generation HMOS microprocessor, introduced in 1978, is typically represented by the Intel 8086 and the Motorola 68000, which are 16-bit microprocessors.

During the 1980s, fourth-generation HCMOS and BICMOS (a combination of bipolar and HCMOS) 32-bit microprocessors evolved. Intel introduced the first commercial 32-bit microprocessor, the problematic Intel 432, which was eventually discontinued. Since 1985, more 32-bit microprocessors have been introduced. These include Motorola's 68020, 68030, 68040, 68060, and PowerPC; Intel's 80386, 80486, and Pentium family, Core Duo, and Core2 Duo microprocessors.

The performance offered by the 32-bit microprocessor is more comparable to that of superminicomputers such as Digital Equipment Corporation's VAX11/750 and VAX11/780. Intel and Motorola also introduced RISC microprocessors: the Intel 80960 and Motorola 88100/PowerPC, which had simplified instruction sets. Note that the purpose of RISC microprocessors is to maximize speed by reducing clock cycles per instruction. Almost all computations can be obtained from a simple instruction set. Note that, in order to enhance performance significantly, Intel Pentium Pro and other succeeding members of the Pentium family and Motorola 68060 are designed using a combination of RISC and CISC.

Single-chip microcomputers such as the Intel 8048 evolved during the '80s. Soon afterward, based on the concept of single-chip microcomputers, Intel introduced the first 8-bit microcontroller—the Intel 8051, which uses Harvard architecture. The 8051 is designed using CISC. The 8051 contains a CPU, memory, I/O, A/D and D/A converters, a timer, and a serial communication interface—all in a single chip. The microcontrollers became popular during the '80s.

The 8-bit microcontrollers are small enough for many embedded applications, but also powerful enough to allow a lot of complexity and flexibility in the design process of an embedded system. Several billion 8-bit microcontrollers were sold during the last decade. Several contemporary microcontroller manufacturers use RISC architecture, and thus provide a cost effective approach. In addition, typical 8-bit microcontrollers such as the PIC18F implemented several on-chip enhanced peripheral functions including PWM (pulse-width modulation) and flash memories. Note that the Motorola/Freescale popular 8-bit microcontroller HC11 does not have on-chip flash memory and PWM functions. PWM is a very desirable feature for applications such as automotive and motor control. These applications may include driving servo motors. In HC11, a timer section is used to generate PWM signals. However, Motorola/Freescale implemented these features in the HC12, which is a 16-bit microcontroller. Note that the HC11 has been popular because of its rich instruction set.

Like EEPROM, flash memory can be programmed and erased electrically. Flash memory is very popular these days compared to EEPROM. Note that EEPROM can be erased one byte at a time while flash memory can be erased only in blocks.

Table 1.1 provides a comparison of some of the basic features of some of the typical microcontrollers.

Microchip has introduced several different versions of the PIC18F microcontroller over the years. All members of the PIC18F family basically contain the same instruction set. However, certain features such as memory sizes, number of I/O ports, A/D channels, and PWM modules may vary from one version to another. In this book, a specific PIC18F chip such as the PIC18F4321 will be considered in detail.

#### 1.4 Typical Microcontroller Applications

Some of the typical microcontroller applications include the following:

- automotive systems

- operation of devices such as a microwave oven, a radiator fan in a car, or servo motors used to move the handles on a foosball table

- barcode readers

- hotel card key writers

- robotics

In the following discussion, a microcontroller-based temperature control system is first described. Since microcontrollers are widely used as "embedded controllers" in embedded applications, the basic concepts associated with embedded controllers are then considered.

| IADLE 1.1                 | Comparison of       | Dasic leatures of  | typical interocon  | roners                               |

|---------------------------|---------------------|--------------------|--------------------|--------------------------------------|

|                           | PIC18F              | MSP 430            | HC11               | AVR                                  |

| Manufacturer              | Microchip           | Texas              | Motorola /         | Atmel                                |

|                           | Technology          | Instruments        | Freescale          |                                      |

| Introduced                | 2000; the first     | Late 1990s         | 1985               | 1996                                 |

|                           | PIC in 1989         |                    |                    |                                      |

| Size                      | 8-bit               | 16-bit             | 8-bit              | 8-bit                                |

| Architecture              | Harvard             | von Neumann        | von Neumann        | Harvard                              |

| Design approach           | RISC                | RISC               | CISC               | RISC                                 |

| On-chip flash<br>memory   | Yes                 | Yes                | No                 | Yes. First to offer<br>on-chip flash |

| On-chip PWM               | Yes.                | Yes                | No                 | Yes                                  |

| CPU Clock                 | 40-MHz<br>(maximum) | 1-MHz<br>(maximum) | 4-MHz<br>(maximum) | 20-MHz<br>(maximum)                  |

| Total Instructions        | 75                  | 27                 | 144                | 123                                  |

| Total Addressing<br>modes | 6                   | 7                  | 6                  | 5                                    |

TABLE 1.1

Comparison of basic features of typical microcontrollers

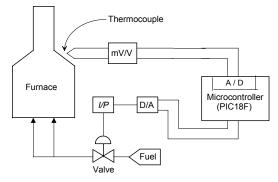

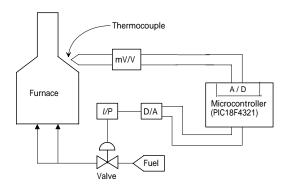

#### FIGURE 1.1 Furnace temperature control

#### 1.4.1 A Simple Microcontroller Application

To put microcontrollers into perspective, it is important to explore a simple application. For example, consider the microcontroller-based dedicated controller shown in Figure 1.1. Suppose that it is necessary to maintain the temperature of a furnace to a desired level to maintain the quality of a product. Assume that the designer has decided to control this temperature by adjusting the fuel. This can be accomplished using a typical microcontroller such as the PIC18F along with the interfacing components as follows. Temperature is an analog (continuous) signal. It can be measured by a temperature-sensing (measuring) device such as a thermocouple. The thermocouple provides the measurement in millivolts (mV) equivalent to the temperature.

Since microcontrollers only understand binary numbers (0's and 1's), each analog mV signal must be converted to a binary number using the microcontroller's on-chip analog-to-digital (A/D) converter. Note that the PIC18F contains an on-chip A/D converter. The PIC18F does not include an on-chip digital-to-analog (D/A) converter. However, the D/A converter chip can be interfaced to the PIC18F externally.

First, the millivolt signal is amplified by a mV/V amplifier to make the signal compatible for A/D conversion. A microcontroller such as the PIC18F can be programmed to solve an equation with the furnace temperature as an input. This equation compares the temperature measured with the temperature desired, which can be entered into the microcontroller using the keyboard. The output of this equation will provide the appropriate opening and closing of the fuel valve to maintain the appropriate temperature. Since this output is computed by the microcontroller, it is a binary number. This binary output must be converted into an analog current or voltage signal.

The D/A (digital-to-analog) converter chip inputs this binary number and converts it into an analog current (I). This signal is then input into the current/pneumatic (I/P) transducer for opening or closing the fuel input valve by air pressure to adjust the fuel to the furnace. The furnace temperature desired can thus be achieved. Note that a transducer converts one form of energy (electrical current in this case) to another form (air pressure in this example).

#### 1.4.2 Embedded Controllers

Embedded microcontroller systems, also called embedded controllers, are designed to manage specific tasks. Once programmed, the embedded controllers can manage the functions of a wide variety of electronic products. In embedded applications, the microcontrollers are embedded in the host system; their presence and operation are basically hidden from the host system.

Typical embedded control applications include office automation products such as copiers, laser products, fax machines, and consumer electronics such as VCRs and microwave ovens. Applications such as printers typically utilize a microcontroller. The RISC microcontrollers are ideal for these types of applications. Note that the personal computer interfaced to the printer is the host.

RISC microcontrollers such as the PIC18F are well suited for applications including robotics, controls, instrumentation, and consumer electronics. The key features of the RISC microcontrollers that make them ideal for these applications are their relatively low level of integration in the chip, and instruction pipeline architecture. These characteristics result in low power consumption, fast instruction execution, and fast recognition of interrupts.

Although microcontrollers including PIC18F are considered ideal for many embedded applications, sometimes they might not be able to perform certain tasks. For example, applications such as laser printers require a high performance microprocessor with on-chip floating-point hardware. The PowerPC RISC microprocessor with on-chip floating-point hardware is ideal for these types of applications. Note that the personal computer interfaced to the laser printer is the host. The PIC18F will not be suitable for such an application since it does not provide floating-point instructions.

# 2 microcontroller basics

In this chapter we describe the fundamental material needed to understand the basic characteristics of microcontrollers. It includes topics such as typical microcontroller architectures, timing signals, CPU organization, and status flags. An overview of pipelining and RISC vs. CISC is included. Finally, an introduction to the functional characteristics of the PIC18F is included.

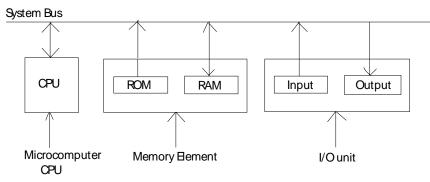

#### 2.1 Basic Blocks of a Microcomputer

In order to understand the functions performed by typical modules contained in a microcontroller, it is necessary to cover the basic blocks of a microcomputer.

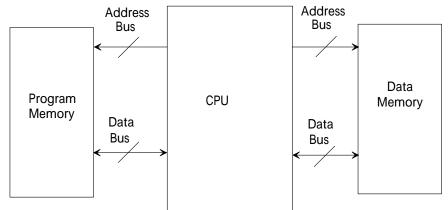

A microcomputer has three basic blocks: a microprocessor (CPU on a chip), a memory unit, and an input/output (I/O) unit. Figure 2.1 shows the basic blocks of a microcomputer. A system bus (comprised of several wires) connects these blocks. The CPU executes all the instructions and performs arithmetic and logic operations on data. The CPU of the microcomputer contains all the registers and the control unit, as well as arithmetic-logic circuits of the microcomputer.

A *memory unit* stores both data and instructions. The memory section typically contains ROM and RAM chips. The ROM can only be read and is nonvolatile; that is, it retains its contents when the power is turned off. A ROM is typically used to store instructions and data that do not change. For example, it might store a table of seven-segment codes for outputting data to a display external to the microcomputer for turning on a digit from 0 through 9.

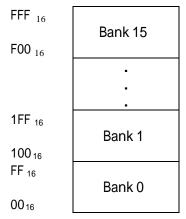

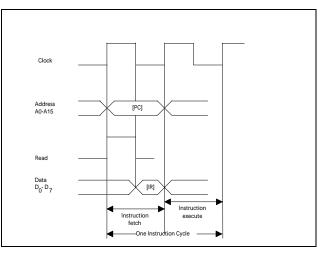

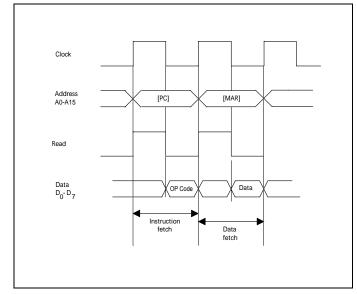

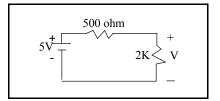

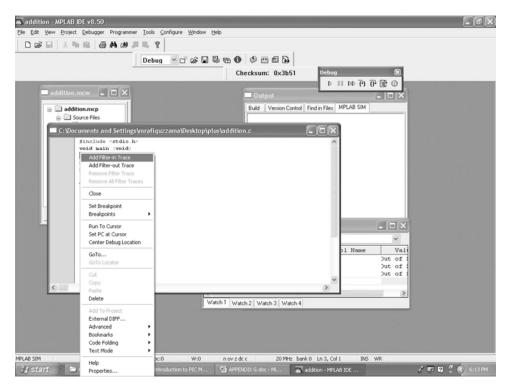

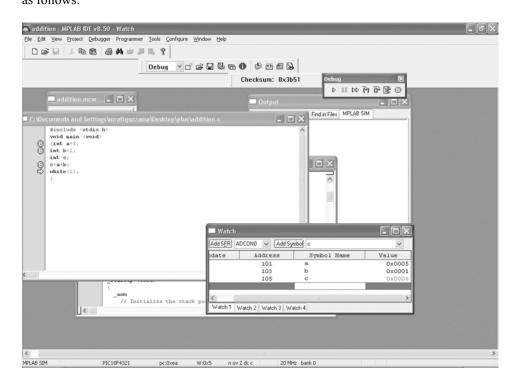

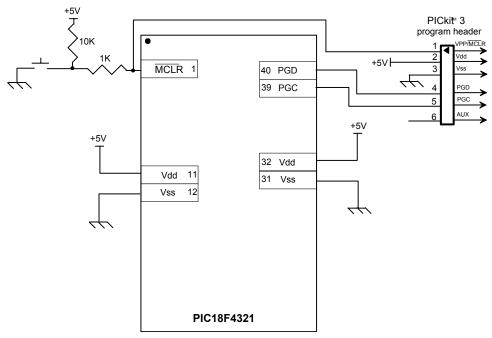

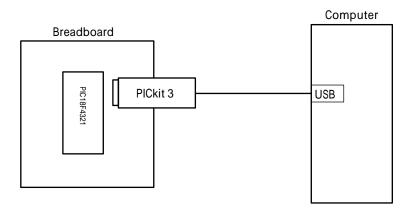

One can read from and write into a RAM. The RAM is volatile; that is, it does not retain its contents when the power is turned off. A RAM is used to store programs and data that are temporary and might change during the course of executing a program. An *I/O unit* transfers data between the microcomputer and the external devices via I/O ports (registers). The transfer involves data, status, and control signals.